大多数现代 circuit design 都依赖于 logic receiver 的精确 logic signals。这种保证基于对信号路径阻抗的精心设计,包括印刷电路板 (PCB) 传输线、互连、通孔和电缆。

如果您设计了基于 PCB 叠层的受控阻抗传输线,您如何知道 PCB 制造公司或其他供应商是否构建了您的叠层以满足您的受控阻抗规格?事实上,即使在与各种层压板制造商讨论之后,我们发现供应商数据表中指定的大多数介电常数都具有不确定性,并且存在很大可变性。这会产生一个号召性用语,以测量这些材料以使其正确。

TDR 的工作原理

时域反射计 (TDR) 测量信号通过某种传输环境(如电路板走线、电缆、连接器等)传播时产生的反射。由于 TDR 使用示波器测量电压反射曲线,因此该曲线可以转换为阻抗曲线,从而可以测量传输线的特性阻抗和传播延迟。TDR 是一个很好的工具,可用于鉴定供应商堆栈,例如确定介电常数 (Dk) 阻抗的变化。

信号路径长度、信号传播时间和介电常数 (Dk) 都是相关的。如果我们知道这三个中的任何两个,我们就可以使用 TDR 来求解第三个。请记住,距离等于速度乘以时间。如果我们使用一个定义的结构,其中我们知道传输线的物理长度,那么我们可以测量传播时间并计算介电常数。

首先,了解信号如何通过介质传播非常重要。首先,让我们重申真空中光速的定义,它是一个常数,由 (1) 表示。这也是信号在真空中传播的速度。

使用 (1),我们可以计算相速度 (Vp) 通过有损介质传输的信号,有时称为传播速度:

从 EQ(2) 中,可以推导出信号传播时间,其定义如下:

TDR 测量信号的反射,因此信号必须通过信号路径往返。为了确定传输线的物理长度,我们将单向行程除以系数 2。这在 EQ(4) 中显示。

解决 D 的 EQ(4)k,得到 EQ(5),可用于计算有效 Dk.TDR 用于测量已知距离内的信号往返行程。如图 1 所示,被测设备 (DUT) 上的信号路径之一 (TP5-TP6) 包括两个相距正好 3 英寸的“标记”,如丝印上所示。

图 1 – J2154A 12GHz 差分 TDR 附带的 Picotest TDR 演示板的描述。

快速回顾一下,传输线或波导由麦克斯韦方程组定义的 E 场和 H 场组成。对于由两个或多个导体组成的传输线,传播模式是横向电磁 (TEM) 波。其特点是

并且这些场在形式上类似于均匀区域中的平面波 [2]。这很重要,因为 TEM 波传播是 PCB 技术中最常见的;然而,也有其他波 [3]。

微带线由两根导体组成,其几何形状如图 2 所示。宽度 (w) 的导体印在规定厚度 (h) 的层压板上。参考图 2 并按照 [2] 中的定义,如果介电常数 (Ɛr) = 1,则会出现均质介质(空气)中的双导体溶液。这将构成一条具有相速度的 TEM 传输线

然而,在微带线中,信号看到的介电常数并不是层压板的体积值。与带状线不同,微带不包含在均匀介电区域内这一事实使事情变得复杂。微带传输线的精确磁场构成了混合横向磁横电 (TM-TE) 波,这需要更先进的分析技术 [2]。要理解这一点,我们需要考虑微带的电场 (E) 和磁场 (H) 是如何存在于非均匀电介质中的。如图 2 所示。

图 2 – 微带线的几何形状以及微带 E 和 H 场线的描述。

对于更实际的应用,如 [2] 所示,可以使用近似值来计算介电常数。在这种情况下,信号看到一个有效介电常数(有效介电常数 Ɛ伊芙),它由 EQ(6) 所示的近似值表示。

模拟层压板的 Dkeff

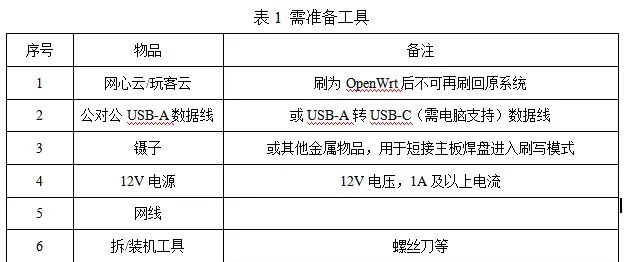

图 1 所示的 Picotest TDR 演示板是使用 Rogers RO4003C 的两层 PCB,在 10GHz 时的典型 Dk 为 3.38+/-0.05 [4]。由于演示板使用 8 mil 厚度的层压板,因此公布的块体 Dk 为 3.803。Rogers Corporation 在使用其 MWI 计算器时,还将已发布的体块 Dk 称为设计 Dk。根据 Rogers 的说法,Design Dk 没有公差,因为它取决于厚度、铜类型或表面粗糙度、频率和一些 PCB 制造公差。TDR 演示板的指定 PCB 叠层如图 3 所示,标记为 TP5 的 3 英寸走线的指定走线宽度(如图 1 所示)为 14.9 mils。

如图 7 和图 8 所示,对 TDR 演示板进行了横截面分析,以确定确切的制造尺寸。横截面结果如图 4 所示。参考图 3,PCB 为 2 层,通常由 0.203 mm 厚的 RO4003C 层压板和 0.6 mm 厚的 FR-4 背衬组成,以获得更好的刚度并有助于防止 PCB 卷曲。报告的实际 PCB 成品总厚度为 0.741 毫米,比指定的总叠层厚度薄 62 微米。不幸的是,从报告的横截面来看,我们无法确定 RO4003C 材料层压板、FR-4 材料层压板的实际制造厚度或层压板厚度的变化。但是,我们确实知道RO4003C的制造公差为 8 mil +/- 1 mil (0.20 mm +/- 0.03 mm) [5]。这些公布的制造公差允许层压材料厚度有 12% 的变化。

图 4 – TDR 演示板横截面信息。

如图 5 所示,我们 PCB 的有效 Dk 是使用 Keysight PathWave ADS 的一部分,使用受控阻抗线路设计器(CILD)[6] 中的 2D 求解器进行仿真。ADS 的结果表明,有效介电常数为 Dk伊芙= 2.869 的。

图 5 – Keysight PathWave ADS 受控阻抗线路设计器。

使用罗杰斯在线 MWI 计算器进行二次检查,并输入相同的参数,如图 6 [7] 所示。罗杰斯 MWI 计算器得出 Dk伊芙= 2.8255,与 PathWave ADS Controlled Impedance Line Designer 的 2.869 结果相差不到 1.5%。

如图所示,我们使用 ADS 和 MWI 计算器计算的有效 Dk 结果几乎相同,因此我们对结果有很高的信心。但是,根据 PCB 设计中传输信号的频率,这些值可能会也可能不会提供足够的保证,从而严格控制您的阻抗。这背后的原因是,设计 Dk 没有公差,因为它取决于厚度、铜类型或表面粗糙度以及 PCB 制造公差 [8]。

图 6 – Picotest 演示板的 Rogers MWI 计算器结果。

使用 TDR 测量层压板的 Dkeff

具有 Dk 的预期结果伊芙定义,让我们测量 TDR 演示板上的 3 英寸走线,以便与仿真结果进行比较。

对于此测量,我们使用 Picotest J2154A TDR 和泰克 MSO68B 示波器,并使用 Picotest P2105A、16.5 GHz 带宽、40mil 间距 TDR 探头来接触 DUT。

在进一步讨论之前,我们先讨论一下如何确定 TDR 的分辨率限制。根据 IPC-TM-650 2.5.5.7 [9],TDR 分辨率限值定义为总系统上升时间和传播速度的函数。

哪里:

trSYS (英语)= TDR 系统上升时间或下降时间,10% 至 90%

Vp= 信号传播速度

在这种测量设置中,示波器、探头和 TDR 转换时间会影响测得的信号的上升时间和下降时间。因此,必须将示波器、探头和 TDR 视为一个系统,以得出真实的系统上升时间。为了确定总系统上升时间,我们可以计算平方和,如 EQ(8) 所示。

每个组件的上升时间信息可以在相应的数据表中找到。对于 J2154A TDR,trTDR= 30 次。对于 MSO68B,tr范围= 40 次。对于 P2105A (16.5 GHz) TDR 探头,tr探针= 21.21 次因此由 EQ(8)、trSYS (英语)是

分辨率与脉冲边沿和传播速度有关。传播发生在有效 Dk (D凯夫).因此,参考 EQ(2) 和 EQ(9),J2154A TDR,带 MSO68B,使用 P2105A TDR 探头,带 D凯夫= 2.82,根据图 6 所示的 MWI 结果,计算结果为:

这个分辨率限制告诉我们,使用这个 TDR 系统,我们可以以足够的保真度在电上解析结构之间的最小距离。换句话说,如果 TDR 系统的上升时间不够快,两个靠得很近的不连续性可能会重叠,从而难以区分传输线上的结构 [10]。由于演示板上的两个铜迹线标记在演示板走线上相距 3 英寸(3000 mil),因此我们知道使用这种 TDR 测量设置可以获得足够的分辨率。

这些铜标记中的每一个都显示为电容式的,因为它们比信号走线宽。每个标记的结果是阻抗下降。由于我们知道标记的确切分离,因此我们可以测量阻抗骤降之间的往返时间,以获得精确的信号传播时间。

如图 7 和图 8 中的设置以及图 9 中捕获的结果所示,测量了两个标记之间的往返时间,发现为 883.066 ps。MSO68B 上的增量时间测量精度 (DTA) 以 [11] 为 327.78 fs。这为测量增加了不到 0.04% 的总误差。在我们的测量设置中,信号轨迹、数学函数和光标提取都是平均的,大大提高了这种精度。如果不进行校准,50 Ω 端口阻抗的容差是主要误差。测量频率、试样长度和测量位置也由 IPC-TM-650 2.5.5.7 [9] 定义。

图 7 – 使用 Picotest P2105A TDR 探头和 J2154A 差分 PerfectPulse® TDR 和泰克 MSO68B 示波器对 3000 mil 迹线进行 TDR 测量设置。

图 8 – 使用演示板 TP5 走线和 P2105A TDR 探头的 TDR 测量设置。

图 9 – 使用 P2105A 探头对演示板 TP5 Trace 进行 TDR 测量。

如图 10 所示,TP5-TP6 走线的平均阻抗是通过测量 20% 至 80% 点之间的传输平均阻抗为 51.54Ω 来得出的。用于计算此阻抗结果的方法已经详细说明了 [1]。但是,需要注意的是,此测量设置使用数学函数,包括对信号迹线进行平均和光标提取,这大大提高了测量信噪比 (SNR),从而提高了有效位数 (ENOB) 和分辨率。

TDR 的工作原理

时域反射计 (TDR) 测量信号通过某种传输环境(如电路板走线、电缆、连接器等)传播时产生的反射。由于 TDR 使用示波器测量电压反射曲线,因此该曲线可以转换为阻抗曲线,从而可以测量传输线的特性阻抗和传播延迟。TDR 是一个很好的工具,可用于鉴定供应商堆栈,例如确定介电常数 (Dk) 阻抗的变化。

信号路径长度、信号传播时间和介电常数 (Dk) 都是相关的。如果我们知道这三个中的任何两个,我们就可以使用 TDR 来求解第三个。请记住,距离等于速度乘以时间。如果我们使用一个定义的结构,其中我们知道传输线的物理长度,那么我们可以测量传播时间并计算介电常数。

首先,了解信号如何通过介质传播非常重要。首先,让我们重申真空中光速的定义,它是一个常数,由 (1) 表示。这也是信号在真空中传播的速度。

使用 (1),我们可以计算相速度 (Vp) 通过有损介质传输的信号,有时称为传播速度:

从 EQ(2) 中,可以推导出信号传播时间,其定义如下:

TDR 测量信号的反射,因此信号必须通过信号路径往返。为了确定传输线的物理长度,我们将单向行程除以系数 2。这在 EQ(4) 中显示。

解决 D 的 EQ(4)k,得到 EQ(5),可用于计算有效 Dk.TDR 用于测量已知距离内的信号往返行程。如图 1 所示,被测设备 (DUT) 上的信号路径之一 (TP5-TP6) 包括两个相距正好 3 英寸的“标记”,如丝印上所示。

图 1 – J2154A 12GHz 差分 TDR 附带的 Picotest TDR 演示板的描述。

快速回顾一下,传输线或波导由麦克斯韦方程组定义的 E 场和 H 场组成。对于由两个或多个导体组成的传输线,传播模式是横向电磁 (TEM) 波。其特点是

并且这些场在形式上类似于均匀区域中的平面波 [2]。这很重要,因为 TEM 波传播是 PCB 技术中最常见的;然而,也有其他波 [3]。

微带线由两根导体组成,其几何形状如图 2 所示。宽度 (w) 的导体印在规定厚度 (h) 的层压板上。参考图 2 并按照 [2] 中的定义,如果介电常数 (Ɛr) = 1,则会出现均质介质(空气)中的双导体溶液。这将构成一条具有相速度的 TEM 传输线

然而,在微带线中,信号看到的介电常数并不是层压板的体积值。与带状线不同,微带不包含在均匀介电区域内这一事实使事情变得复杂。微带传输线的精确磁场构成了混合横向磁横电 (TM-TE) 波,这需要更先进的分析技术 [2]。要理解这一点,我们需要考虑微带的电场 (E) 和磁场 (H) 是如何存在于非均匀电介质中的。如图 2 所示。

图 2 – 微带线的几何形状以及微带 E 和 H 场线的描述。

对于更实际的应用,如 [2] 所示,可以使用近似值来计算介电常数。在这种情况下,信号看到一个有效介电常数(有效介电常数 Ɛ伊芙),它由 EQ(6) 所示的近似值表示。

模拟层压板的 Dkeff

图 1 所示的 Picotest TDR 演示板是使用 Rogers RO4003C 的两层 PCB,在 10GHz 时的典型 Dk 为 3.38+/-0.05 [4]。由于演示板使用 8 mil 厚度的层压板,因此公布的块体 Dk 为 3.803。Rogers Corporation 在使用其 MWI 计算器时,还将已发布的体块 Dk 称为设计 Dk。根据 Rogers 的说法,Design Dk 没有公差,因为它取决于厚度、铜类型或表面粗糙度、频率和一些 PCB 制造公差。TDR 演示板的指定 PCB 叠层如图 3 所示,标记为 TP5 的 3 英寸走线的指定走线宽度(如图 1 所示)为 14.9 mils。

如图 7 和图 8 所示,对 TDR 演示板进行了横截面分析,以确定确切的制造尺寸。横截面结果如图 4 所示。参考图 3,PCB 为 2 层,通常由 0.203 mm 厚的 RO4003C 层压板和 0.6 mm 厚的 FR-4 背衬组成,以获得更好的刚度并有助于防止 PCB 卷曲。报告的实际 PCB 成品总厚度为 0.741 毫米,比指定的总叠层厚度薄 62 微米。不幸的是,从报告的横截面来看,我们无法确定 RO4003C 材料层压板、FR-4 材料层压板的实际制造厚度或层压板厚度的变化。但是,我们确实知道RO4003C的制造公差为 8 mil +/- 1 mil (0.20 mm +/- 0.03 mm) [5]。这些公布的制造公差允许层压材料厚度有 12% 的变化。

图 4 – TDR 演示板横截面信息。

如图 5 所示,我们 PCB 的有效 Dk 是使用 Keysight PathWave ADS 的一部分,使用受控阻抗线路设计器(CILD)[6] 中的 2D 求解器进行仿真。ADS 的结果表明,有效介电常数为 Dk伊芙= 2.869 的。

图 5 – Keysight PathWave ADS 受控阻抗线路设计器。

使用罗杰斯在线 MWI 计算器进行二次检查,并输入相同的参数,如图 6 [7] 所示。罗杰斯 MWI 计算器得出 Dk伊芙= 2.8255,与 PathWave ADS Controlled Impedance Line Designer 的 2.869 结果相差不到 1.5%。

如图所示,我们使用 ADS 和 MWI 计算器计算的有效 Dk 结果几乎相同,因此我们对结果有很高的信心。但是,根据 PCB 设计中传输信号的频率,这些值可能会也可能不会提供足够的保证,从而严格控制您的阻抗。这背后的原因是,设计 Dk 没有公差,因为它取决于厚度、铜类型或表面粗糙度以及 PCB 制造公差 [8]。

图 6 – Picotest 演示板的 Rogers MWI 计算器结果。

使用 TDR 测量层压板的 Dkeff

具有 Dk 的预期结果伊芙定义,让我们测量 TDR 演示板上的 3 英寸走线,以便与仿真结果进行比较。

对于此测量,我们使用 Picotest J2154A TDR 和泰克 MSO68B 示波器,并使用 Picotest P2105A、16.5 GHz 带宽、40mil 间距 TDR 探头来接触 DUT。

在进一步讨论之前,我们先讨论一下如何确定 TDR 的分辨率限制。根据 IPC-TM-650 2.5.5.7 [9],TDR 分辨率限值定义为总系统上升时间和传播速度的函数。

哪里:

trSYS (英语)= TDR 系统上升时间或下降时间,10% 至 90%

Vp= 信号传播速度

在这种测量设置中,示波器、探头和 TDR 转换时间会影响测得的信号的上升时间和下降时间。因此,必须将示波器、探头和 TDR 视为一个系统,以得出真实的系统上升时间。为了确定总系统上升时间,我们可以计算平方和,如 EQ(8) 所示。

每个组件的上升时间信息可以在相应的数据表中找到。对于 J2154A TDR,trTDR= 30 次。对于 MSO68B,tr范围= 40 次。对于 P2105A (16.5 GHz) TDR 探头,tr探针= 21.21 次因此由 EQ(8)、trSYS (英语)是

分辨率与脉冲边沿和传播速度有关。传播发生在有效 Dk (D凯夫).因此,参考 EQ(2) 和 EQ(9),J2154A TDR,带 MSO68B,使用 P2105A TDR 探头,带 D凯夫= 2.82,根据图 6 所示的 MWI 结果,计算结果为:

这个分辨率限制告诉我们,使用这个 TDR 系统,我们可以以足够的保真度在电上解析结构之间的最小距离。换句话说,如果 TDR 系统的上升时间不够快,两个靠得很近的不连续性可能会重叠,从而难以区分传输线上的结构 [10]。由于演示板上的两个铜迹线标记在演示板走线上相距 3 英寸(3000 mil),因此我们知道使用这种 TDR 测量设置可以获得足够的分辨率。

这些铜标记中的每一个都显示为电容式的,因为它们比信号走线宽。每个标记的结果是阻抗下降。由于我们知道标记的确切分离,因此我们可以测量阻抗骤降之间的往返时间,以获得精确的信号传播时间。

如图 7 和图 8 中的设置以及图 9 中捕获的结果所示,测量了两个标记之间的往返时间,发现为 883.066 ps。MSO68B 上的增量时间测量精度 (DTA) 以 [11] 为 327.78 fs。这为测量增加了不到 0.04% 的总误差。在我们的测量设置中,信号轨迹、数学函数和光标提取都是平均的,大大提高了这种精度。如果不进行校准,50 Ω 端口阻抗的容差是主要误差。测量频率、试样长度和测量位置也由 IPC-TM-650 2.5.5.7 [9] 定义。

图 7 – 使用 Picotest P2105A TDR 探头和 J2154A 差分 PerfectPulse® TDR 和泰克 MSO68B 示波器对 3000 mil 迹线进行 TDR 测量设置。

图 8 – 使用演示板 TP5 走线和 P2105A TDR 探头的 TDR 测量设置。

图 9 – 使用 P2105A 探头对演示板 TP5 Trace 进行 TDR 测量。

如图 10 所示,TP5-TP6 走线的平均阻抗是通过测量 20% 至 80% 点之间的传输平均阻抗为 51.54Ω 来得出的。用于计算此阻抗结果的方法已经详细说明了 [1]。但是,需要注意的是,此测量设置使用数学函数,包括对信号迹线进行平均和光标提取,这大大提高了测量信噪比 (SNR),从而提高了有效位数 (ENOB) 和分辨率。

如果您设计了基于 PCB 叠层的受控阻抗传输线,您如何知道 PCB 制造公司或其他供应商是否构建了您的叠层以满足您的受控阻抗规格?

暂无评论内容