深入了解前沿FPGA开发技术的技术特点

关键词:FPGA开发技术、前沿技术特点、可编程逻辑、并行计算、高速接口

摘要:本文旨在深入探讨前沿FPGA开发技术的技术特点。首先介绍了FPGA开发的背景知识,包括目的、预期读者、文档结构和相关术语。接着详细阐述了FPGA的核心概念与联系,包括其架构和工作原理,并通过Mermaid流程图进行展示。分析了核心算法原理及具体操作步骤,结合Python代码进行说明。同时介绍了相关的数学模型和公式,并举例说明。通过项目实战,展示了开发环境搭建、源代码实现和代码解读。探讨了FPGA的实际应用场景,推荐了学习资源、开发工具框架和相关论文著作。最后总结了未来发展趋势与挑战,并给出常见问题解答和扩展阅读参考资料,帮助读者全面深入地了解前沿FPGA开发技术的特点。

1. 背景介绍

1.1 目的和范围

FPGA(Field – Programmable Gate Array),即现场可编程门阵列,作为一种重要的可编程逻辑器件,在现代电子系统设计中扮演着至关重要的角色。本文的目的在于深入剖析前沿FPGA开发技术的技术特点,涵盖FPGA的架构、编程方式、应用领域等多个方面。范围不仅包括传统的FPGA开发技术,还着重已关注近年来出现的新趋势和新技术,如基于AI的FPGA设计优化、高速接口技术、低功耗设计等。通过全面的分析,帮助读者了解FPGA开发技术的最新发展动态,为实际的开发工作提供理论支持和实践指导。

1.2 预期读者

本文预期读者主要包括电子工程师、FPGA开发人员、相关专业的学生以及对FPGA技术感兴趣的技术爱好者。对于有一定FPGA开发基础的工程师和开发人员,本文可以帮助他们深入了解前沿技术,拓宽技术视野,提升开发能力;对于学生而言,本文可以作为学习FPGA开发的参考资料,帮助他们构建完整的知识体系;对于技术爱好者,本文能够让他们对FPGA开发技术有一个全面而深入的认识,激发他们进一步探索的兴趣。

1.3 文档结构概述

本文将按照以下结构展开:首先介绍FPGA开发技术的背景知识,包括术语和相关概念;接着阐述FPGA的核心概念与联系,通过文本示意图和Mermaid流程图进行详细说明;然后分析核心算法原理和具体操作步骤,并结合Python代码进行解释;介绍相关的数学模型和公式,并举例说明其应用;通过项目实战展示FPGA开发的实际过程;探讨FPGA的实际应用场景;推荐学习资源、开发工具框架和相关论文著作;最后总结未来发展趋势与挑战,提供常见问题解答和扩展阅读参考资料。

1.4 术语表

1.4.1 核心术语定义

FPGA:现场可编程门阵列,是一种可以在现场进行编程配置的集成电路,由可编程逻辑块、可编程互连资源和可编程输入输出块组成。

可编程逻辑块(CLB):FPGA中实现逻辑功能的基本单元,包含查找表(LUT)、触发器等元件,可以实现各种组合逻辑和时序逻辑功能。

可编程互连资源:用于连接各个可编程逻辑块和输入输出块,实现信号的传输和路由。

查找表(LUT):一种基于真值表的组合逻辑实现方式,通过存储不同输入组合对应的输出值,实现逻辑函数的计算。

片上系统(SoC):在FPGA中集成处理器、存储器、外设等多种功能模块,形成一个完整的系统。

1.4.2 相关概念解释

硬件描述语言(HDL):用于描述数字电路和系统的语言,常见的有Verilog和VHDL。通过HDL可以对FPGA的逻辑功能进行建模和设计。

综合:将HDL代码转换为门级网表的过程,综合工具会根据目标FPGA的架构和资源,对代码进行优化和映射。

布局布线:将综合得到的门级网表映射到FPGA的具体物理资源上,并进行信号的布线,确定各个逻辑单元和互连资源的位置。

比特流文件:经过布局布线后生成的文件,包含了FPGA的配置信息,通过下载比特流文件可以将设计配置到FPGA芯片中。

1.4.3 缩略词列表

FPGA:Field – Programmable Gate Array

CLB:Configurable Logic Block

LUT:Look – Up Table

SoC:System on a Chip

HDL:Hardware Description Language

2. 核心概念与联系

2.1 FPGA架构原理

FPGA的基本架构主要由可编程逻辑块(CLB)、可编程互连资源和可编程输入输出块(IOB)组成。可编程逻辑块是实现逻辑功能的核心单元,它可以通过编程配置实现各种组合逻辑和时序逻辑。可编程互连资源用于连接各个逻辑块和输入输出块,使得信号能够在芯片内部进行传输和交换。可编程输入输出块则负责芯片与外部电路的接口,实现信号的输入和输出。

下面是一个简单的文本示意图,展示了FPGA的基本架构:

+---------------------+

| |

| 可编程逻辑块 |

| |

+---------------------+

| |

| 可编程互连资源 |

| |

+---------------------+

| |

| 可编程输入输出块 |

| |

+---------------------+

2.2 FPGA工作原理

FPGA的工作原理基于硬件描述语言(HDL)的编程和配置。开发人员使用HDL(如Verilog或VHDL)描述所需的逻辑功能,然后通过综合工具将HDL代码转换为门级网表。接着,布局布线工具将门级网表映射到FPGA的具体物理资源上,并生成比特流文件。最后,将比特流文件下载到FPGA芯片中,完成配置,使得FPGA能够实现预定的逻辑功能。

以下是一个简单的Mermaid流程图,展示了FPGA的工作流程:

2.3 核心概念联系

可编程逻辑块、可编程互连资源和可编程输入输出块之间相互协作,共同实现FPGA的逻辑功能。可编程逻辑块根据开发人员的设计实现具体的逻辑运算,可编程互连资源将各个逻辑块连接起来,形成一个完整的逻辑电路,可编程输入输出块则负责与外部世界进行信息交互。硬件描述语言、综合、布局布线和比特流文件的生成是FPGA开发过程中的关键环节,它们紧密相连,缺一不可。通过HDL代码描述逻辑功能,经过综合和布局布线生成比特流文件,最终将比特流文件下载到FPGA芯片中,实现硬件逻辑的配置和运行。

3. 核心算法原理 & 具体操作步骤

3.1 算法原理

在FPGA开发中,常见的算法包括逻辑综合算法和布局布线算法。

3.1.1 逻辑综合算法

逻辑综合算法的目标是将HDL代码转换为门级网表,同时对逻辑电路进行优化。其中一种常用的算法是基于布尔代数的算法。例如,对于一个简单的逻辑函数 F = A ⋅ B + A ⋅ C ‾ F = A cdot B + A cdot overline{C} F=A⋅B+A⋅C,可以使用布尔代数的规则进行化简:

F = A ⋅ B + A ⋅ C ‾ = A ⋅ ( B + C ‾ ) egin{align*} F&=A cdot B + A cdot overline{C}\ &=A cdot (B+overline{C}) end{align*} F=A⋅B+A⋅C=A⋅(B+C)

逻辑综合工具会根据FPGA的资源特点,将化简后的逻辑函数映射到查找表(LUT)等可编程逻辑资源上。

3.1.2 布局布线算法

布局布线算法的主要任务是将综合得到的门级网表映射到FPGA的具体物理资源上,并进行信号的布线。一种常见的布局算法是模拟退火算法。模拟退火算法是一种基于概率的全局优化算法,它通过模拟固体退火的过程,在解空间中搜索最优解。在布局问题中,模拟退火算法会随机交换逻辑单元的位置,根据一定的概率接受更差的解,以避免陷入局部最优解。

3.2 具体操作步骤

3.2.1 逻辑综合操作步骤

以下是使用Python模拟简单逻辑综合的示例代码:

# 定义逻辑函数

def logic_function(A, B, C):

return (A and B) or (A and (not C))

# 布尔代数化简后的函数

def simplified_function(A, B, C):

return A and (B or (not C))

# 测试逻辑函数

A = True

B = False

C = True

result1 = logic_function(A, B, C)

result2 = simplified_function(A, B, C)

print(f"原始逻辑函数结果: {

result1}")

print(f"化简后逻辑函数结果: {

result2}")

在实际的FPGA开发中,逻辑综合通常使用专业的综合工具,如Xilinx Vivado或Altera Quartus等。开发人员只需要编写HDL代码,然后使用综合工具进行综合操作,工具会自动完成逻辑化简和门级网表的生成。

3.2.2 布局布线操作步骤

虽然布局布线算法较为复杂,难以用简单的Python代码实现,但可以通过以下步骤进行理解:

初始化布局:随机将逻辑单元分配到FPGA的物理资源上。

计算代价函数:评估当前布局的优劣,通常考虑布线长度、资源利用率等因素。

随机交换逻辑单元位置:根据模拟退火算法的规则,随机交换两个逻辑单元的位置。

计算新的代价函数:评估交换后布局的优劣。

接受或拒绝新布局:根据一定的概率接受更差的布局,以避免陷入局部最优解。

重复步骤3 – 5:直到满足终止条件,如达到最大迭代次数或代价函数收敛。

在实际开发中,布局布线通常由专业的布局布线工具完成,开发人员只需要设置相关的参数,工具会自动进行布局布线操作。

4. 数学模型和公式 & 详细讲解 & 举例说明

4.1 布尔代数模型

布尔代数是FPGA逻辑设计的基础,它定义了逻辑变量和逻辑运算的规则。布尔代数中的基本逻辑运算包括与( ⋅ cdot ⋅)、或( + + +)、非( ‾ overline{} )。

4.1.1 基本公式

交换律: A + B = B + A A + B = B + A A+B=B+A, A ⋅ B = B ⋅ A A cdot B = B cdot A A⋅B=B⋅A

结合律: ( A + B ) + C = A + ( B + C ) (A + B)+C = A+(B + C) (A+B)+C=A+(B+C), ( A ⋅ B ) ⋅ C = A ⋅ ( B ⋅ C ) (A cdot B)cdot C = Acdot(B cdot C) (A⋅B)⋅C=A⋅(B⋅C)

分配律: A ⋅ ( B + C ) = A ⋅ B + A ⋅ C A cdot (B + C)=A cdot B+A cdot C A⋅(B+C)=A⋅B+A⋅C, A + ( B ⋅ C ) = ( A + B ) ⋅ ( A + C ) A+(B cdot C)=(A + B)cdot(A + C) A+(B⋅C)=(A+B)⋅(A+C)

互补律: A + A ‾ = 1 A+overline{A}=1 A+A=1, A ⋅ A ‾ = 0 Acdotoverline{A}=0 A⋅A=0

同一律: A + 0 = A A + 0 = A A+0=A, A ⋅ 1 = A A cdot 1 = A A⋅1=A

零律: A + 1 = 1 A + 1 = 1 A+1=1, A ⋅ 0 = 0 A cdot 0 = 0 A⋅0=0

4.1.2 举例说明

假设有一个逻辑函数 F = ( A + B ) ⋅ ( A + C ) F = (A + B)cdot(A + C) F=(A+B)⋅(A+C),可以使用分配律进行化简:

F = ( A + B ) ⋅ ( A + C ) = A ⋅ A + A ⋅ C + B ⋅ A + B ⋅ C = A + A ⋅ C + A ⋅ B + B ⋅ C = A ( 1 + C + B ) + B ⋅ C = A + B ⋅ C egin{align*} F&=(A + B)cdot(A + C)\ &=Acdot A+Acdot C + Bcdot A + Bcdot C\ &=A+Acdot C + Acdot B + Bcdot C\ &=A(1 + C + B)+Bcdot C\ &=A + Bcdot C end{align*} F=(A+B)⋅(A+C)=A⋅A+A⋅C+B⋅A+B⋅C=A+A⋅C+A⋅B+B⋅C=A(1+C+B)+B⋅C=A+B⋅C

4.2 代价函数模型

在布局布线算法中,代价函数用于评估布局的优劣。一个常见的代价函数可以考虑布线长度和资源利用率。

设 L L L 为总布线长度, U U U 为资源利用率,则代价函数 C C C 可以定义为:

C = α L + β U C = alpha L+eta U C=αL+βU

其中 α alpha α 和 β eta β 是权重系数,用于调整布线长度和资源利用率在代价函数中的重要性。

4.2.1 举例说明

假设在一个FPGA布局中,总布线长度 L = 100 L = 100 L=100,资源利用率 U = 0.8 U = 0.8 U=0.8, α = 0.6 alpha = 0.6 α=0.6, β = 0.4 eta = 0.4 β=0.4,则代价函数的值为:

C = 0.6 × 100 + 0.4 × 0.8 = 60 + 0.32 = 60.32 egin{align*} C&=0.6 imes100 + 0.4 imes0.8\ &=60+0.32\ &=60.32 end{align*} C=0.6×100+0.4×0.8=60+0.32=60.32

通过比较不同布局的代价函数值,可以选择代价函数值最小的布局作为最优布局。

5. 项目实战:代码实际案例和详细解释说明

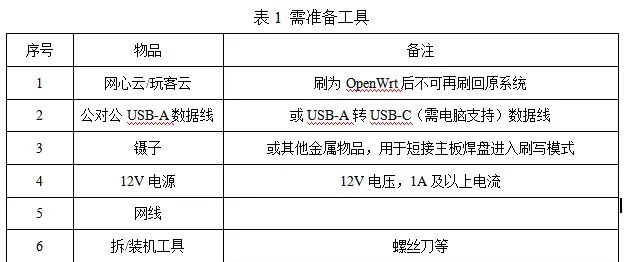

5.1 开发环境搭建

5.1.1 选择FPGA开发板

本次项目实战选择Xilinx Artix – 7开发板,该开发板具有丰富的资源和接口,适合初学者和专业开发者使用。

5.1.2 安装开发工具

安装Xilinx Vivado开发套件,该套件包含了综合、布局布线、仿真等一系列工具,是FPGA开发的常用工具。

5.1.3 配置开发环境

打开Xilinx Vivado,创建一个新的项目,选择对应的FPGA芯片型号,配置开发板的约束文件,确保开发环境能够正常工作。

5.2 源代码详细实现和代码解读

5.2.1 设计一个简单的计数器

以下是使用Verilog语言实现的一个简单的计数器代码:

module counter (

input wire clk,

input wire rst,

output reg [3:0] count

);

always @(posedge clk or posedge rst) begin

if (rst) begin

count <= 4'b0000;

end else begin

count <= count + 1;

end

end

endmodule

5.2.2 代码解读

模块定义:module counter 定义了一个名为 counter 的模块,该模块有三个端口:clk 是时钟信号,rst 是复位信号,count 是4位计数器输出。

时序逻辑:always @(posedge clk or posedge rst) 表示该块代码在时钟信号的上升沿或复位信号的上升沿触发。

复位操作:当 rst 信号为高电平时,计数器 count 被复位为 4'b0000。

计数操作:当 rst 信号为低电平时,计数器 count 在每个时钟上升沿加1。

5.3 代码解读与分析

5.3.1 功能分析

该计数器模块实现了一个简单的4位计数器功能,在时钟信号的驱动下,计数器的值不断加1。当复位信号有效时,计数器被复位为0。

5.3.2 资源使用分析

在Xilinx Vivado中,可以通过综合报告查看该计数器模块的资源使用情况。一般来说,该模块主要使用了一些查找表(LUT)和触发器(FF)资源。

5.3.3 时序分析

通过时序分析工具,可以分析该计数器模块的时序性能,确保时钟信号和复位信号的时序满足要求,避免出现时序违规的情况。

6. 实际应用场景

6.1 通信领域

6.1.1 高速数据传输

FPGA可以实现高速的数据收发和处理,在光纤通信、无线通信等领域得到广泛应用。例如,在5G通信中,FPGA可以用于基站的信号处理和数据传输,实现高速的数据包转发和协议处理。

6.1.2 通信协议转换

不同的通信设备可能使用不同的通信协议,FPGA可以实现协议转换的功能。例如,将以太网协议转换为CAN总线协议,实现不同设备之间的通信。

6.2 工业控制领域

6.2.1 运动控制

FPGA可以实现高精度的运动控制,如机器人的关节控制、数控机床的运动控制等。通过FPGA可以实现快速的算法运算和实时的控制信号输出,提高运动控制的精度和稳定性。

6.2.2 工业自动化

在工业自动化生产线中,FPGA可以用于传感器数据采集、逻辑控制和设备监控等。例如,对生产线上的温度、压力等传感器数据进行实时采集和处理,根据预设的逻辑规则控制设备的运行。

6.3 人工智能领域

6.3.1 深度学习推理

FPGA可以用于深度学习模型的推理加速。与传统的CPU和GPU相比,FPGA具有低功耗、高并行性的特点,能够实现高效的深度学习推理。例如,在智能安防领域,FPGA可以用于人脸识别、目标检测等算法的实时推理。

6.3.2 算法加速

FPGA可以对一些复杂的算法进行加速,如矩阵运算、卷积运算等。在人工智能研究中,FPGA可以作为一种加速工具,提高算法的运行效率。

7. 工具和资源推荐

7.1 学习资源推荐

7.1.1 书籍推荐

《FPGA设计实战演练:Verilog HDL版》:这本书详细介绍了FPGA设计的基础知识和实践技巧,通过大量的实例帮助读者掌握Verilog HDL语言和FPGA设计流程。

《Xilinx FPGA设计权威指南》:针对Xilinx FPGA进行深入讲解,包括FPGA的架构、开发工具的使用、设计优化等方面的内容。

《数字设计和计算机体系结构》:涵盖了数字电路设计的基础知识,对于理解FPGA的逻辑设计原理有很大的帮助。

7.1.2 在线课程

Coursera上的“FPGA Design for Embedded Systems”:该课程由知名高校的教授授课,系统地介绍了FPGA设计的相关知识和技能。

中国大学MOOC上的“FPGA原理及应用”:适合国内学习者,课程内容丰富,讲解详细。

7.1.3 技术博客和网站

FPGAer.cn:国内专业的FPGA技术论坛,提供了丰富的技术文章、资料下载和交流社区。

Xilinx官方博客:Xilinx公司发布的关于FPGA技术的最新动态和应用案例。

7.2 开发工具框架推荐

7.2.1 IDE和编辑器

Xilinx Vivado:Xilinx公司推出的FPGA开发套件,集成了综合、布局布线、仿真等多种功能,是Xilinx FPGA开发的首选工具。

Altera Quartus Prime:Intel(原Altera)公司的FPGA开发工具,支持Altera系列FPGA的开发。

Visual Studio Code:一款轻量级的代码编辑器,支持Verilog和VHDL语言的语法高亮和代码调试,可与开发工具集成使用。

7.2.2 调试和性能分析工具

ChipScope:Xilinx公司的在线逻辑分析仪,可用于实时监测FPGA内部信号的状态,帮助开发人员进行调试。

Sigasi Studio:一款专门用于HDL代码编辑和调试的工具,提供了强大的代码分析和调试功能。

7.2.3 相关框架和库

IP核:FPGA开发中常用的知识产权核,如以太网IP核、USB IP核等,可以大大缩短开发周期。

HLS(高级综合)工具:如Xilinx Vivado HLS,可以将C/C++代码转换为硬件描述语言,提高开发效率。

7.3 相关论文著作推荐

7.3.1 经典论文

“A Survey of FPGA – Based Reconfigurable Computing Systems”:对FPGA在可重构计算系统中的应用进行了全面的综述。

“FPGA – Based Acceleration of Deep Neural Networks”:探讨了FPGA在深度学习加速方面的应用和技术。

7.3.2 最新研究成果

可以通过IEEE Xplore、ACM Digital Library等学术数据库搜索关于FPGA开发技术的最新研究成果,了解行业的前沿动态。

7.3.3 应用案例分析

一些知名企业和研究机构会发布FPGA应用案例分析报告,如Xilinx公司的应用案例文档,这些案例可以帮助读者了解FPGA在实际项目中的应用和解决方案。

8. 总结:未来发展趋势与挑战

8.1 未来发展趋势

8.1.1 与AI技术深度融合

未来FPGA将与人工智能技术深度融合,用于深度学习模型的训练和推理加速。FPGA的高并行性和低功耗特点使其在AI领域具有很大的应用潜力,能够实现更高效的算法运算和实时处理。

8.1.2 异构计算架构

FPGA将与CPU、GPU等其他计算设备组成异构计算架构,充分发挥各自的优势,提高系统的整体性能。例如,在数据中心中,FPGA可以作为协处理器,处理一些特定的计算任务,减轻CPU和GPU的负担。

8.1.3 低功耗设计

随着物联网和移动设备的发展,对FPGA的低功耗设计要求越来越高。未来FPGA将采用更先进的工艺和设计技术,降低功耗,延长设备的续航时间。

8.2 挑战

8.2.1 设计复杂度增加

随着FPGA技术的不断发展,其功能和性能不断提升,设计复杂度也越来越高。开发人员需要掌握更多的知识和技能,才能完成复杂的FPGA设计任务。

8.2.2 工具和技术更新换代快

FPGA开发工具和技术更新换代非常快,开发人员需要不断学习和掌握新的工具和技术,才能跟上行业的发展步伐。

8.2.3 竞争压力大

FPGA市场竞争激烈,不同厂商之间的产品和技术竞争不断加剧。FPGA厂商需要不断创新和提高产品性能,才能在市场中占据一席之地。

9. 附录:常见问题与解答

9.1 FPGA与ASIC有什么区别?

FPGA是现场可编程的逻辑器件,可以在开发过程中进行多次编程和修改;而ASIC是专用集成电路,一旦制造完成就无法修改。FPGA的开发周期短、成本低,适合小批量生产和快速原型验证;ASIC的性能高、功耗低,适合大规模生产。

9.2 如何选择合适的FPGA开发板?

选择FPGA开发板需要考虑以下因素:芯片型号、资源规模、接口类型、开发工具支持等。根据项目的需求和预算,选择合适的FPGA开发板。例如,如果项目需要高速数据传输,可以选择具有高速接口的开发板;如果是初学者,可以选择资源规模较小、价格较低的开发板。

9.3 FPGA开发中如何进行时序优化?

时序优化可以从以下几个方面入手:合理规划逻辑设计,减少逻辑级数;优化布局布线,缩短信号传输路径;调整时钟频率和时钟偏移等。在Xilinx Vivado等开发工具中,也提供了一些时序优化的功能和工具,可以帮助开发人员进行时序优化。

9.4 FPGA开发需要掌握哪些编程语言?

FPGA开发主要使用硬件描述语言(HDL),如Verilog和VHDL。此外,还可以学习一些脚本语言,如Tcl,用于自动化开发流程。对于高级综合(HLS)开发,还需要掌握C/C++语言。

10. 扩展阅读 & 参考资料

10.1 扩展阅读

《FPGA高级设计技术》:深入介绍了FPGA的高级设计技巧和方法,适合有一定基础的开发人员阅读。

《FPGA数字信号处理》:介绍了FPGA在数字信号处理领域的应用和实现方法。

10.2 参考资料

Xilinx官方文档:Xilinx公司提供的关于FPGA开发工具和芯片的详细文档,是FPGA开发的重要参考资料。

Altera官方文档:Intel(原Altera)公司的FPGA开发文档,对于使用Altera系列FPGA的开发人员有很大的帮助。

IEEE相关论文:IEEE出版的关于FPGA技术的研究论文,涵盖了FPGA的各个方面,是了解FPGA前沿技术的重要途径。

暂无评论内容