我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。

老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:

做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老好人主义。

不觉间来到夏初六月,横坐在电脑前,敲击点文字,对自己也算一个时间的记忆,多年后再次点击,也期待那时会像触发记忆的闸口,让现在的这点岁月传递至那时那刻。

一、背景信息

在汽车智能化进程如疾风骤雨般推进的当下,整车电子电气(EE)架构正经历着一场深刻变革,从早期的分布式电子控制单元(ECU)架构逐步迈向集中式域控制器架构,并持续朝着中央集成式架构的方向大步迈进。

回溯分布式ECU架构阶段,微控制器单元(MCU)宛如汽车电子系统的“智慧大脑”,承担着计算与控制的核心重任。彼时,汽车的功能相对单一,各ECU独立运行,负责特定的控制任务,MCU凭借其稳定的性能和较低的成本,满足了当时的计算需求。

随着汽车智能化水平的不断攀升,集中式域控制器架构应运而生。在这一阶段,汽车的功能日益复杂,各种传感器和执行器产生的数据量呈爆炸式增长,传统MCU芯片在面对大量异构数据的吞吐以及更快的数据处理需求时,显得力不从心。就好比一条狭窄的河道难以承载汹涌的洪水,传统MCU芯片的处理能力已无法满足汽车智能化发展的需求。

在此背景下,系统级芯片(SoC)芯片凭借其卓越的数据传输效率和强大的算力,脱颖而出,成为域控制器主控芯片的不二之选。SoC芯片如同一位身怀绝技的“全能选手”,将多个功能模块集成于一体,能够高效地处理来自不同传感器的数据,实现更快速、更精准的计算和控制,为汽车的智能化功能提供了坚实的硬件支撑。

目前,车载SoC芯片主要聚焦于两大关键应用领域:智能驾驶和智能座舱。在智能驾驶领域,SoC芯片需要具备强大的图像处理、传感器融合和决策规划能力,以实现对车辆周围环境的精准感知和智能决策,保障行车安全。而在智能座舱领域,SoC芯片则要支持高清显示、多屏互动、语音交互等丰富功能,为用户打造舒适、便捷、智能的驾乘体验。

尽管现阶段座舱SoC芯片和智驾SoC芯片仍处于独立发展的阶段,各自专注于不同的应用场景和技术要求,但汽车产业发展的趋势已清晰可见。随着整车架构朝着更集中的跨域融合架构演进,以及车企在架构设计和软件开发能力上的不断提升,智能座舱和智能驾驶的融合将是大势所趋。这种融合将不再局限于上层应用的简单叠加,而是会逐步深入到下层的硬件层面,实现硬件资源的共享和协同工作。

车载SoC芯片也必将顺应这一融合趋势,进行迭代升级。未来的车载SoC芯片将不再局限于单一的功能领域,而是朝着舱驾一体SoC甚至中央计算SoC的方向发展。舱驾一体SoC将整合智能座舱和智能驾驶的功能,实现硬件资源的统一调配和优化利用,提高系统的整体性能和效率。而中央计算SoC则将成为汽车电子系统的核心枢纽,集中处理来自各个域的数据和任务,为汽车提供更强大的计算能力和更智能的决策支持。届时,舱驾一体SoC和中央计算SoC将逐渐成为市场的主流产品形态,引领汽车智能化发展进入一个新的时代。

二、车载 SoC 芯片基本介绍

在汽车智能化浪潮的席卷下,整车电子电气(EE)架构正经历着从分布式电子控制单元(ECU)架构,向集中式域控制器架构的升级转变,并持续朝着中央集成式架构的方向大步迈进。在分布式 ECU 架构时代,微控制器单元(MCU)宛如汽车电子系统的“核心大脑”,承担着计算与控制的关键任务。然而,随着汽车智能化水平的不断提高,集中式域控制器架构应运而生,汽车功能日益复杂,各类传感器和执行器产生的数据量呈爆发式增长,传统 MCU 芯片在处理大量异构数据的吞吐以及快速数据处理方面,已显得力不从心,如同小马拉大车,难以满足当下需求。在此背景下,数据传输效率更高、算力更强的系统级芯片(SoC)芯片,凭借其卓越性能,成为域控制器主控芯片的必然之选。

1、基础定义

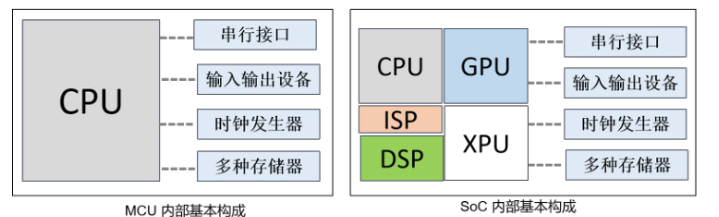

车规级计算芯片依据集成规模可分为 MCU 和 SoC 两大类。MCU 又被称作“单片机芯片”,其内部集成了处理器、存储器、输入/输出接口以及其他外设,常应用于控制任务相对简单、实时性要求较高的嵌入式系统。车载 MCU 通常运行的操作系统有 AUTOSAR CP 和 FreeRTOS,一般不支持运行高复杂度的操作系统。

与之相比,SoC 芯片作为系统级芯片,内部集成了更多的异构处理单元,结构设计更为复杂,处理和计算能力也更为强大,适用于多任务处理以及计算任务更为复杂的应用场景。车载 SoC 能够运行更为复杂的操作系统,如 QNX、Linux、Android 和 AUTOSAR AP 等。

2、硬件构成

车载 SoC 芯片内部通常包含处理器、存储器、外设 I/O 等几大核心模块。车载 SoC 芯片内部的处理器通常涵盖以下几种单元模块:

-> 通用逻辑运算单元:一般基于 CPU 实现,主要负责逻辑运算任务,承担着管理软硬件资源、任务调度以及外部资源访问等职责,实现系统层面的功能逻辑、诊断逻辑以及影子模式数据挖掘等功能。一些典型应用包括基于优化的决策规划算法、车辆控制算法等。

-> AI 加速单元:通常基于神经网络处理器(NPU)实现,承担大规模浮点数并行计算需求,作为神经网络算法的加速器,主要负责处理 AI 方面的计算任务。

-> 图像/视频处理单元:通常基于数字信号处理器(DSP)、图像信号处理器(ISP)、图形处理器(GPU)等处理器实现。ISP 作为视觉处理芯片,主要功能是对摄像头输出的图像信号进行调校,涵盖自动曝光(AE)、自动对焦(AF)、自动白平衡(AWB)、图像去噪等操作;DSP 是一种具有特殊结构的微处理器,相较于通用 CPU,更适用于计算密集度高的处理工作,典型应用包括传统的计算机视觉(CV)图像处理、一些自定义算子的加速处理等;GPU 具有强大的浮点运算能力,主要用于图像的 3D 渲染和拼接等应用。

-> 硬件安全模块(HSM):用于为应用程序提供加解密服务,管理敏感信息和资产,保护加密密钥等,确保数据的安全性。

-> 安全微控制器(Safety MCU):主要用于实时监控 SoC 内部各硬件模块的状态和通信,一旦出现问题能够及时报错,进而保障整个系统的功能安全性。

3、内部存储器

内部存储器包括易失性存储器和非易失性存储器两大类。

-> 易失性存储器:在断电情况下(如系统正常关闭或意外关闭),数据会丢失,无法继续保留存储数据。它主要用于临时存储正在处理的程序和数据,车载 SoC 内部常用的存储器类型包括静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM,如 DDR、LPDDR 等)。

-> 非易失性存储器:在断电情况下,依然能够保存存储数据,主要用于存放固定数据、固件程序等一般不需要经常改动的数据。车载 SoC 内部常用的存储器类型包括与非闪存(NAND Flash,如 eMMC、UFS 等)和或非闪存(Nor Flash)等。

4、外设 I/O

外设 I/O 包括通用数据接口、摄像头信号接口、音频接口和显示器接口等。

-> 通用数据接口:涵盖 PCIe、LVDS、USB、SATA、CAN/CAN-FD、以太网等,用于实现芯片与外部设备之间的数据传输和通信。

-> 摄像头信号接口:如 MIPI-CSI-2、GMSL、FPD Link 等,用于连接摄像头,实现图像和视频信号的传输。

-> 音频接口:包括 I2S、TDM、SPDIF 等,用于音频信号的输入和输出。

-> 显示器接口:如 DP、HDMI 等,用于连接显示器,实现图像和视频的显示。

三、车载 SoC芯片性能要求

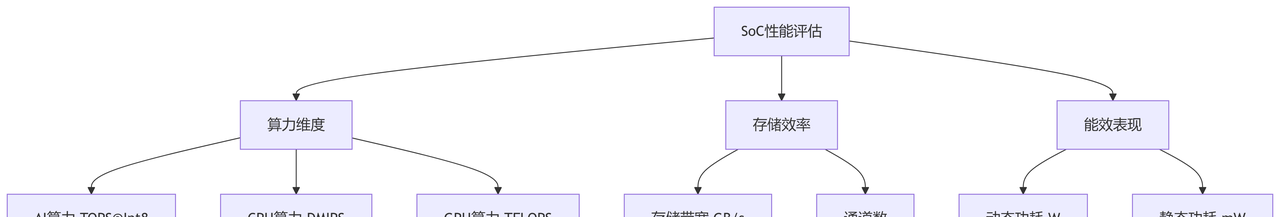

在评估车载 SoC 芯片性能时,需从 AI 算力、CPU 算力、GPU 算力、存储带宽、功耗以及制造工艺等多个维度进行全面考量。

1、AI 算力

AI 算力通常指的是芯片执行乘积累加(MAC)指令的运算能力。MAC 指令操作与数据类型紧密相关,在不同数据精度条件下,所测得的 AI 算力会有较大差异。企业通常宣称的算力是指芯片运算能力的理论峰值,一般以 TOPS 为单位,且默认以 Int8 作为算力量化标准。

我们不能仅仅已关注表面的理论算力数值。在实际应用场景中,芯片真正的有效算力,即“算力利用率”更为关键。以智能驾驶应用为例,SoC 芯片的实际算力利用率会因图片分辨率、网络结构差异等因素而有所不同。例如,高分辨率的图片需要更多的计算资源进行处理,复杂的网络结构也会增加计算的复杂度,从而影响芯片的算力利用率。

2、存储带宽

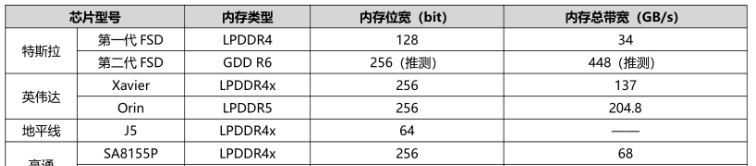

在数据处理过程中,数据需要不断地从存储器单元读取到处理器单元,处理完成后再将结果写回存储器单元。数据在存储器与处理器之间的频繁迁移会带来严重的传输功耗问题。据业内人士指出,AI 运算中 90%的功耗和延迟都源于数据搬运。

芯片的存储带宽由存储器本身的性能和芯片的内存通道数两方面决定。存储带宽的大小直接影响数据搬运的速度和次数,进而在一定程度上决定了芯片的真实算力。如果存储带宽不足,数据搬运速度慢,处理器就需要花费更多时间等待数据,导致芯片的实际算力无法充分发挥。

3、功耗

芯片的功耗包括动态功耗和静态功耗。动态功耗是由于信号值改变而产生的功耗损失,由开关功耗和内部功耗两部分组成。开关功耗是信号在高低电平之间切换时产生的功耗,内部功耗则是芯片内部电路在工作过程中产生的功耗。静态功耗是设备在上电状态但没有信号值改变时消耗的功率。

芯片的功耗与硬件架构、布局布线、工艺制程以及算力大小等因素密切相关。在其他条件相同的情况下,采用的工艺制程越先进,芯片的功耗就越低。例如,更先进的制程可以减小晶体管的尺寸,降低漏电流,从而减少静态功耗。然而,算力越大的芯片,功耗通常也会越大。因为更大的算力需要更多的晶体管参与计算,这会增加芯片的动态功耗。功耗过大不仅会导致芯片发热严重,可能需要安装水冷系统来散热,还会增加整体物料清单(BOM)成本。

车规级要求

根据日常生活中的应用场景,芯片大致可分为消费级、工业级和车规级三大类。由于应用场景不同,芯片在设计、生产、认证等环节的目标设定和实现手段上存在显著差异。与消费级和工业级芯片相比,车规级芯片面临着更恶劣的工作环境、更低的出错容忍率、更长的使用寿命要求以及更久的供货生命周期等挑战。

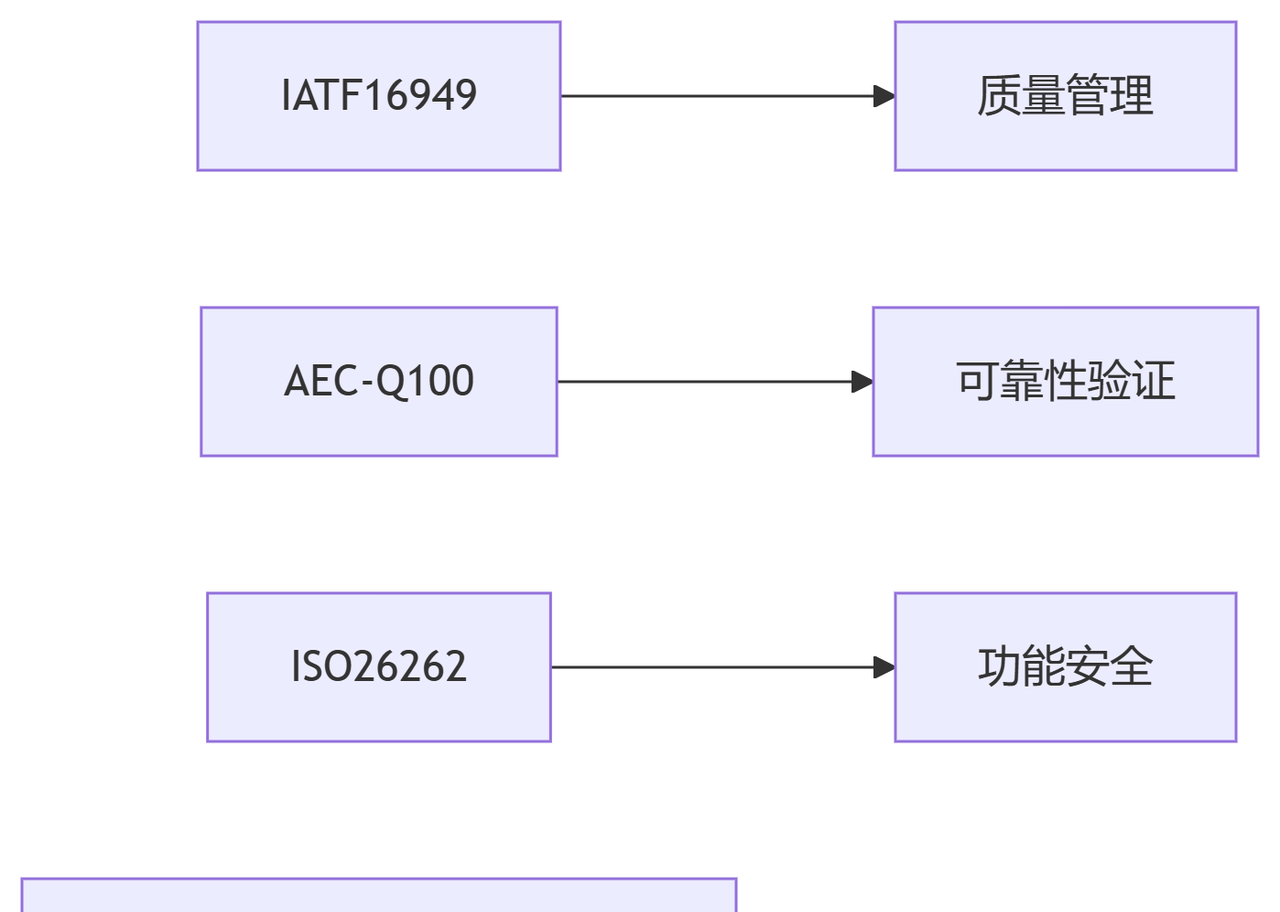

车规级芯片具备高可靠性、高安全性和高稳定性的特点。车载芯片必须经过一系列严格的测试认证,确保其满足车规级相关要求后,才能投入量产。芯片车规认证标准通常涵盖质量管理体系认证 IATF 16949、可靠性标准 AEC – Q100 和功能安全标准 ISO 26262 这三个维度的管控。

-> IATF 16949

IATF 16949 是汽车设计、开发和生产质量管理体系的标准规范。其内容涵盖产品安全风险管理和应急计划、嵌入式软件要求、变更和质保管理以及二级供应商管理等方面。对于车载芯片产品,从芯片设计到流片,再到规模化生产,都需要严格遵循这套管理体系。例如,在产品设计阶段,需要考虑产品的安全性和可靠性,制定相应的风险管理计划;在生产过程中,要确保生产工艺的稳定性和产品质量的可控性。

-> AEC – Q100

AEC – Q100 是车规级元器件通用的可靠性测试标准,也是汽车行业零部件供应商生产的重要参考指南。2023 年 8 月,AEC 发布了 AEC – Q100 的新版测试认证标准文件,这也是目前芯片公司开展 AEC – Q100 测试认证所沿用的最新标准要求。该标准包括 7 大项测试内容:加速环境应力测试、加速寿命测试、封装检验测试、晶圆可靠度验证、电气特性验证、缺陷筛选测试和腔体封装完整性测试。通过这些测试,可以全面评估芯片在不同环境条件下的可靠性和稳定性,确保芯片在汽车恶劣的工作环境中能够正常工作。

-> ISO 26262

ISO 26262 是一项专门针对汽车电子系统的功能安全性制定的国际标准。该标准涵盖了芯片全生命周期的功能安全要求,包括项目需求规划、设计、晶圆制造,最后到封装测试的全过程。其目的是降低芯片在使用中发生故障的风险,确保这些安全关键型设备符合在汽车中使用的要求。例如,在芯片设计阶段,需要采用功能安全设计方法,对芯片进行故障模式、影响和诊断分析(FMEDA),以识别潜在的故障模式,并采取相应的措施来降低故障风险。

四、应用场景

目前,车载 SoC 芯片主要聚焦于两大核心应用领域:智能驾驶与智能座舱。尽管当下座舱 SoC 芯片和智驾 SoC 芯片仍处于独立发展的阶段,但随着整车架构朝着更集中的跨域融合架构持续演进,以及车企在架构设计和软件开发能力方面的不断提升,智能座舱与智能驾驶的融合将逐渐从上层应用层面的融合过渡到下层硬件层面的融合。与此同时,车载 SoC 芯片也必然会顺应两者融合的趋势进行迭代升级。届时,舱驾一体 SoC 乃至中央计算 SoC 将逐步成为市场的主流产品形态。

1、智能座舱

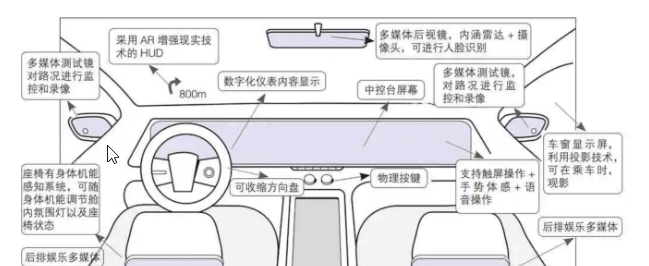

智能座舱是在传统电子座舱的基础上进行全面升级,旨在为用户带来更加智能化、便捷化的乘坐体验和交互体验。通常,智能座舱能够实现车载信息娱乐系统、全液晶仪表系统、抬头显示系统(HUD)、流媒体后视镜(CMS)、车联网系统以及车内乘员监控系统(DMS/OMS)等一系列复杂功能。

这些功能的实现对车载计算芯片提出了严苛的要求。不仅需要芯片具备强大的 CPU 算力,以提升任务处理能力,确保系统高效稳定运行;还需要更强的 GPU 算力,以便高效处理视频、图片等非结构化数据,实现流畅的图像渲染和显示;同时,还需要较大的 AI 算力,满足日益智能化的人机交互体验需求,如语音识别、手势控制等。

传统的 MCU 芯片在算力方面已难以满足智能座舱的多样化需求。因此,智能座舱控制器所使用的主控芯片正逐渐从 MCU 向具有更高集成度、更强算力的 SoC 芯片转变。座舱 SoC 芯片的性能直接决定了座舱域控制器的数据处理能力和图像渲染能力,进而影响座舱内屏显数量、分辨率、运行流畅度,以及舱内交互体验和能够整合的 ADAS 功能数量。

当前,智能座舱的应用场景呈现出以下趋势:

-> 舱内显示:在电子座舱时代,座舱内通常配备小尺寸中控显示屏和物理指针式仪表盘。如今,座舱的中控屏和仪表盘基本都升级为全液晶数字化大屏。部分高端座舱还额外增加了 AR – HUD、流媒体显示屏、后排娱乐屏等,车内显示屏幕正朝着多屏化、大屏化和高清化的方向发展。

-> 舱内交互:舱内交互方式日益多样化。传统电子座舱主要通过物理按键进行交互,而现在舱内物理实体按键逐渐减少,触控式按键、语音交互、手势控制等多态交互方式成为主流,为用户带来更加便捷、自然的交互体验。

-> 舱驾融合:座舱和智驾原本是相互独立的两个部分,如今两者之间的融合日益增多,正逐步从“舱泊一体”向“舱驾一体”演进,实现更深层次的协同与整合。

2、智能驾驶

智能驾驶按照功能体系应用,通常可分为行车和泊车两大类应用场景。在行车场景下,最初采用前视一体机或毫米波雷达模块来实现 L1 等级的基础 ADAS 功能。具体而言:

-> 前视一体机:可实现车道偏离预警(LDW)、车道居中保持(LKA)、交通标识识别(TSR)等功能,帮助驾驶员更好地掌握车辆行驶状态和道路信息。

-> 前置毫米波雷达:能够实现前向碰撞预警(FCW)、自适应巡航控制(ACC)、车辆自动紧急制动(AEB)等功能,有效提升行车安全性。

-> 角毫米波雷达:主要用于实现盲区检测(BSD)、变道辅助(LCA)以及前/后方横向来车碰撞预警(FCTA/RCTA)等功能,为驾驶员提供更全面的周边环境感知。

在上述行车场景应用中,控制芯片一般放置在传感器内部。随着车载 SoC 芯片集成的异构资源日益丰富,以及核心处理器 CPU/GPU/NPU 算力的大幅提升,传感器中的控制芯片逐渐被剥离出来,集成到独立的控制器中完成相应任务。并且,出现了能够独立完成行车和泊车的传感器数据处理、数据融合等软件算法的 SoC 芯片,即所谓的单 SoC 行泊一体方案。

泊车场景最初采用超声波雷达,也被称为“倒车防撞雷达”,主要用于泊车时的防撞提醒。后来,泊车场景中引入摄像头,实现了倒车影像功能。随着技术的不断发展,倒车后视功能升级为 360 全景环视,通过拼接算法对 4 颗环视摄像头分别输出的局部图像进行拼接,最终将拼接好的鸟瞰图传输到中控屏上进行显示,为驾驶员提供更全面的泊车视野。

在泊车场景中,泊车算法的集成形式主要有以下几种:

-> 不带 APA,只有 AVM 功能:泊车算法集成到车机中,实现基础的 360 全景环视功能。

-> 带 APA 和 AVM 功能:泊车算法集成到独立的泊车控制器中,实现自动泊车辅助(APA)和全景环视(AVM)功能。

-> 带 APA 和 AVM 功能,并且配置有座舱域控制器:泊车算法集成到座舱域控制器中,实现泊车功能与座舱系统的深度融合。

-> 除了带 APA 和 AVM 功能外,还带有 HPA 以及 AVP 等功能安全要求比较高的泊车功能:泊车算法集成到智能驾驶域控制器中,通常采用 n*SoC + MCU 的芯片方案,以满足更高的功能安全要求和复杂的泊车算法需求。

其中,第一种和第三种形式是直接集成到座舱相关模块,在此不再赘述。第二种形式在国内刚开始流行时,主机厂的主流方案是基于 TDA2 等小算力 SoC 芯片来完成,但随着技术的发展,这种形式正逐渐被淘汰。

搁笔分享完毕!

愿你我相信时间的力量

做一个长期主义者

© 版权声明

文章版权归作者所有,未经允许请勿转载。如内容涉嫌侵权,请在本页底部进入<联系我们>进行举报投诉!

THE END

暂无评论内容