目录

WCK2CK Synchronization Operation

CAS Command with WCK2CK Synchronization Bits

WCK2CK Sync Operation Followed by a WRITE Command

WCK2CK Sync Operation Followed by a READ Command

WCK2CK Sync Operation with CAS(WS_FS=1)

Rank to Rank WCK2CK Sync Operation

Write Clock Always on Mode (WCK Always on Mode)

参考文献

WCK2CK Synchronization Operation

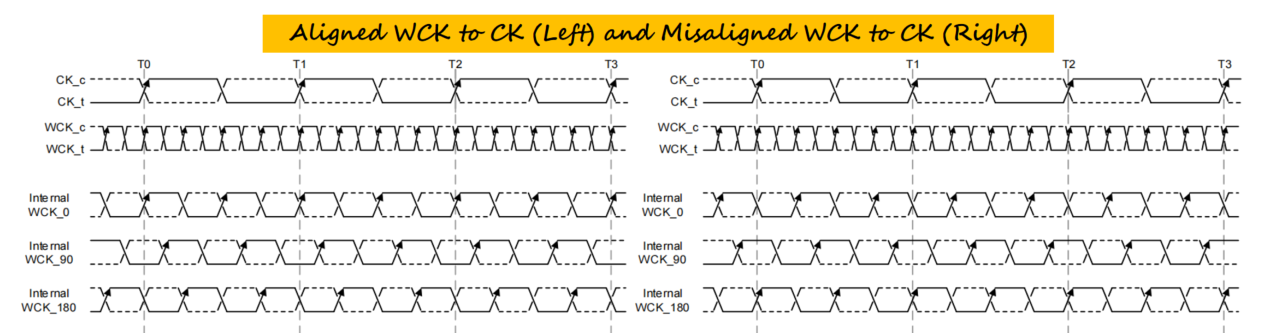

LPDDR5 SDRAM采用两种不同频率的时钟:写时钟(WCK)的频率是命令时钟(CK)的四倍或两倍,这要求LPDDR5 SDRAM在WCK时钟树中集成时钟分频器。通过对WCK进行分频,可将WCK时钟域内SDRAM内部电路的工作速度降低至原来的一半。然而,WCK分频器的初始状态具有不确定性,会导致LPDDR5 SDRAM出现两种不同状态:

与CK时钟对齐的状态(aligned with CK state);

与CK时钟错位的状态(miss-aligned with CK state)。

下图展示了这两种情况。

SDRAM内部的时延控制单元负责将写(WRITE)或读(READ)命令从命令时钟(CK)域转换至写时钟(WCK)域。为实现无差错的时延控制,时延控制电路必须明确SDRAM当前处于与CK时钟对齐状态(aligned with CK state)还是错位状态(miss-aligned with CK state)。LPDDR5 SDRAM可通过WCK2CK同步流程实现状态重置或检测。当存储器控制器发出带有WCK2CK同步标志位的列地址选通(CAS)命令时,控制器会向SDRAM提供半频率的WCK脉冲,以缓解码间干扰(ISI)并优化时序裕量。该操作即定义为WCK2CK同步。

CAS Command with WCK2CK Synchronization Bits

LPDDR5的WCK2CK同步流程由启用了相关位的CAS(列地址选通)命令启动。在发出写入(WRITE)或读取(READ)命令之前,应先发出带有WCK2CK同步功能的CAS命令。下表展示了带有WCK2CK同步位的CAS命令(WS_WR、WS_RD、WS_FS)。当CAS命令中WCK2CK同步标志位为“1”时,表示通知SDRAM需要进行WCK2CK同步。

JEDEC文档中的图67至图70展示了在启用带有WCK2CK同步操作数(WS_WR或WS_RD或WS_FS = 1)的CAS命令时,LPDDR5的WCK2CK同步操作。SDRAM控制器必须在tWCKENL时间之后,以WCK_t & WCK_c 为差分电平的形式开始驱动WCK。WCK2CK同步操作在tWCKENL + tWCKPRE_static时间之后发生,随后在1*tCK时间段内以半速率运行WCK。在WCK2CK同步之前,WCK必须翻转一次,以减少WCK通道中的码间干扰(ISI)。必须在WCK2CK同步之前执行WCK2CK训练。

在发出CAS(WS_WR=1)命令后,应立即紧跟着发出写入(WRITE)命令、发出CAS(WS_RD=1)命令后,也应立即紧跟着发出读取(READ)命令、CAS(WS_FS=1)仅用作独立命令,且可同时向多个存储体组(rank)发出。在WCK2CK同步完成后,WCK必须持续翻转,直至读或写突发传输结束,或者发出CAS(WS_OFF)命令。例如,在退出掉电模式(PDX,Power Down Exit)后,必须在发出写入命令或读取命令之前,先发出启用了WCK2CK同步操作数(WS_WR或WS_RD或WS_FS=1)的CAS命令。因为在掉电期间,WCK2CK同步状态会丢失。

WCK2CK Sync Operation Followed by a WRITE Command

下图展示了紧随WCK2CK同步操作之后立即进行写(WRITE)操作的示例。当CAS WCK2CK同步命令之后紧跟写命令时,该CAS WCK2CK同步命令的WS_WR位将置为1。在CAS(WS_WR=1)命令与写命令之间不允许插入其他命令,必须立即紧跟写命令。tWCKENL_WR是指LPDDR5 SDRAM在接收到WS_WR=1的CAS命令后,为准备WCK2CK同步操作所需的延迟时间。

在图中的Tc1时刻,从WCK2CK同步操作开始算起,满足tWCKENL_WR + tWCKPRE_Static + tWCKPRE_Toggle_WR(这三段时长之和)的条件后,SDRAM控制器启动写数据选通(WRITE DQ)突发传输。传输完成后,经过tWCKPST时长,SDRAM控制器可停止WCK信号的翻转,将WCK驱动器置为高阻抗(Hi-Z)状态,并且为节省功耗,WCK缓冲器也可被关闭。

WCK2CK Sync Operation Followed by a READ Command

下图展示了WCK2CK同步操作后紧跟读(READ)命令的示例。当CAS WCK2CK同步命令之后紧跟读命令时,该CAS WCK2CK同步命令的WS_RD位必须置为1。在CAS(WS_RD=1)命令与读命令之间不允许插入其他命令,必须立即紧跟读命令。tWCKENL_RD是能够保证WCK2CK同步操作顺利完成,并使WCK信号翻转功耗降至最低的最佳延迟时间。

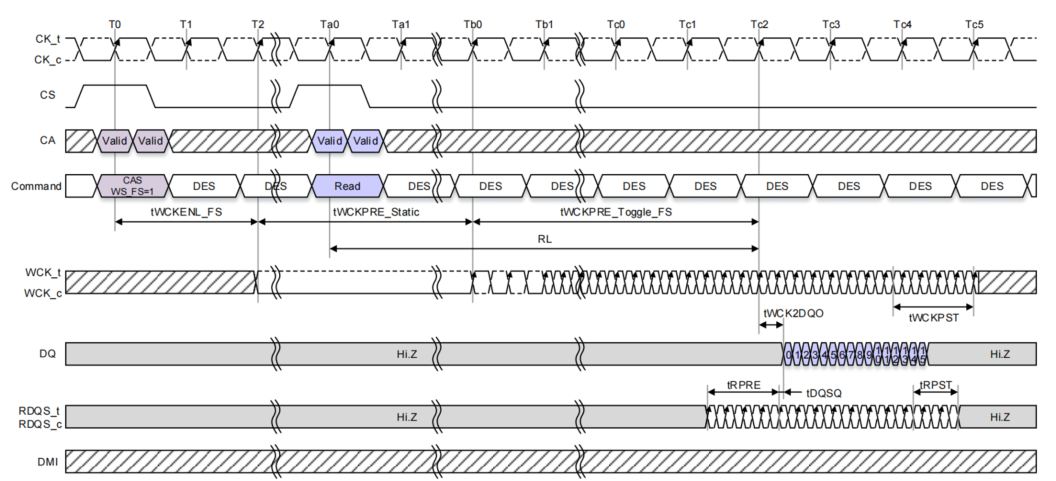

WCK2CK Sync Operation with CAS(WS_FS=1)

当向LPDDR5 SDRAM发出WS_FS=1的CAS命令时,WCK2CK同步操作会以最小延迟tWCKENL_FS执行。通过这种方式,LPDDR5 SDRAM控制器能够尽早将LPDDR5 SDRAM置于WCK2CK同步状态。与CAS(WS_RD/WR)不同,CAS(WS_FS=1)作为独立命令使用,不仅可以向单个存储芯片组(rank)发出,还能同时向多个存储芯片组发出。tWCKPRE_toggle_FS会根据CAS(WS_FS=1)命令与后续读(READ)或写(WRITE)命令之间的指令时序间隔而变化,而tWCKPRE_toggle_WR和tWCKPRE_toggle_RD是以时钟周期(nCK)为单位的精确固定值。在发出CAS(WS_FS=1)命令后,不仅可以发出读/写命令,还可以发出激活(Active)和刷新(Refresh)等其他命令。

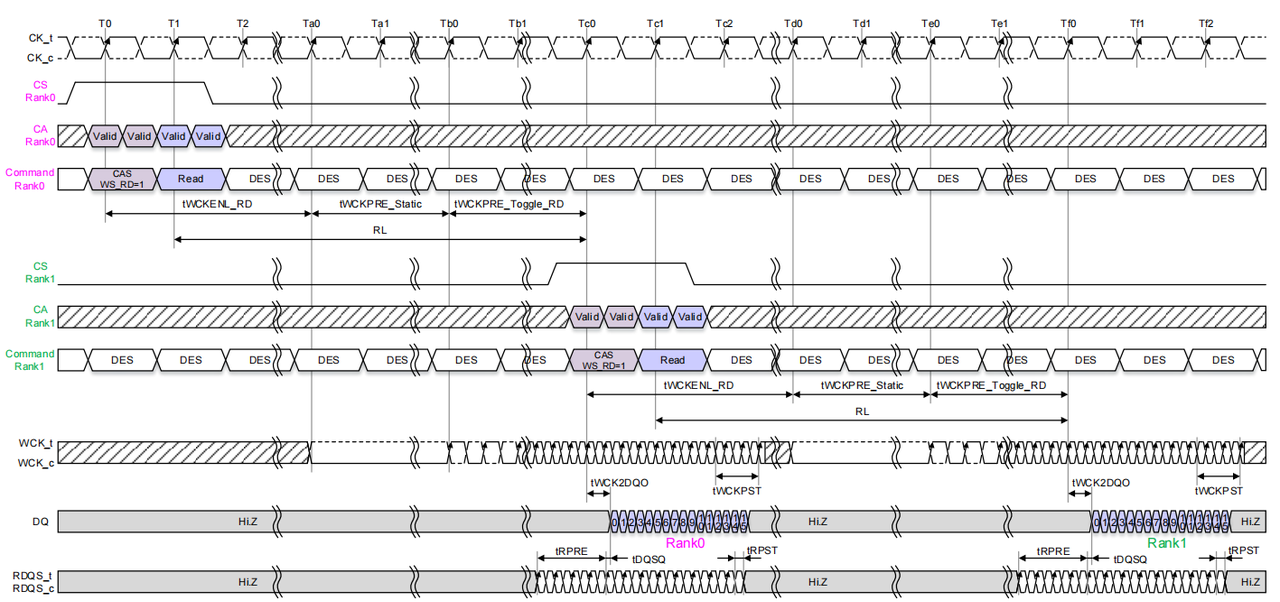

Rank to Rank WCK2CK Sync Operation

存在两种不同的方法来控制双列(two rank)LPDDR5 SDRAM的WCK2CK同步状态:

第一种方法是在完成第0列(rank 0)的DQ数据突发传输后,启动第1列(rank 1)的WCK2CK同步流程,如下图所示,应分别确保第0列的tWCKPST参数和第1列的tWCKPRE参数,以分别满足第0列读取操作中正确的RDQS(读数据选通)后缀时段(post-amble)要求,以及第1列正确的WCK2CK同步操作要求。

第二种方法是如图所示,同时启动两列(both ranks)的WCK2CK同步流程。当两列均未处于WCK2CK同步状态,且两列之间的DQ突发传输已关闭时,考虑到高效利用DQ总线,推荐采用同时发出带有WS_FS=1的CAS命令的方式。

若采用此方法,建议启用WCK Always on Mode(WCK始终开启模式),即设置MR18操作位OP[4]=1B。若未启用该模式,则根据WCK2CK同步关闭时序定义,WCK2CK同步状态将会失效。并且,无论MR18操作位OP[4]的设定情况如何,均可通过CAS(WS_OFF)命令来停止WCK2CK同步。

若某一列(rank)后续的DQ突发传输与另一列先前的DQ突发传输相隔较远,则需考虑因WCK信号切换(toggle)而产生的额外功耗。在完成两列同步后,若不再使用第0列(rank 0),可向第0列发出CAS(WS_OFF)命令以降低功耗。

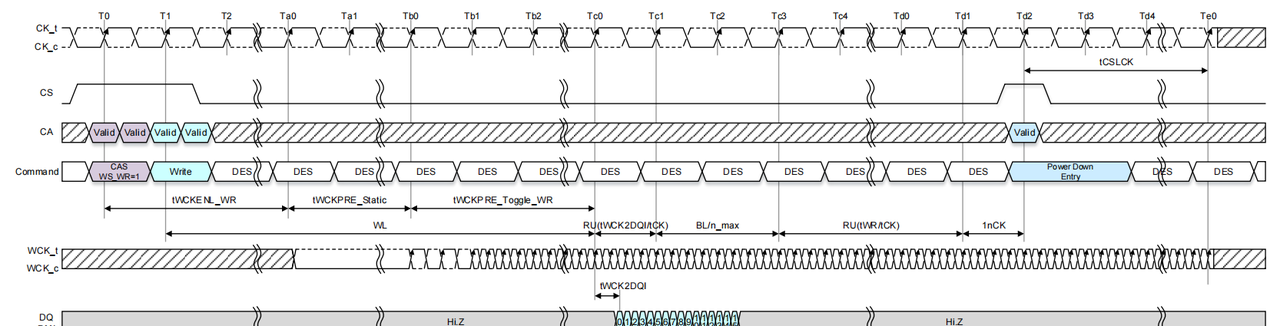

Write Clock Always on Mode (WCK Always on Mode)

LPDDR5 SDRAM将WCK始终开启模式作为模式寄存器设置(MRS)选项予以支持。通过设置MR18操作位OP[4] = 1B,可启用WCK始终开启模式。启用该模式后,LPDDR5 SDRAM中的WCK缓冲器会随WCK2CK同步而开启,并持续保持开启状态,直至SDRAM接收到CAS(WS_OFF)、掉电、自刷新掉电、深度睡眠模式命令或复位信号为止。因此,在WCK2CK同步完成后,无论DQ操作如何,SDRAM控制器都必须使WCK以全速率持续切换。由于进入掉电模式时WCK2CK同步信息会丢失,因此SDRAM控制器在退出掉电模式后、执行DQ操作之前,必须执行WCK2CK同步序列。

下图展示了在WCK2CK同步后接写入命令的WCK始终开启模式时序图。在该时序图中,SDRAM在T0时刻初始处于Bank激活状态,因此SDRAM中的WCK缓冲器处于关闭状态,WCK2CK同步信息丢失。尽管模式寄存器MR18已设置OP[4]=1B(启用WCK始终开启模式),但在接收到带有WCK2CK同步位(WS_WR、WS_RD或WS_FS)置高的CAS命令之前,WCK缓冲器不会开启。在T0时刻,一个WS_WR=1的CAS命令启动了WCK2CK同步流程,并开启了SDRAM中的WCK缓冲器。一旦开启,无论后续收到何种命令,WCK缓冲器都将持续保持开启状态,直至在Td2时刻接收到掉电进入命令。在Td2时刻,掉电进入命令关闭了WCK缓冲器,以降低SDRAM的功耗。

参考文献

[1] JEDEC JESD209-5C: Low Power Double Data Rate LPDDR 5/5X.

欢迎已关注作者的微信公众号,微信中搜索“SI的奇妙世界”,一个纯粹的技术分享和交流平台!

暂无评论内容