PCIe架构概述一

本文插图均引自《PCI Express Technology 3.0》

什么是PCIe?

PCI Express是一种串行总线技术,用于CPU与PCIe设备之间,其前身是并行总线模型的PCI,PCIe在软件上完全兼容PCI。

PCIe的硬件连接

PCIe使用双向连接,能同时发送和接收信息,允许同时双向传输,每个方向是一组差分线(Tx+ Tx- Rx+ Rx-)。设备之间的路径成为链路(Link)由一对或者多对发送和接收组成,其中的一对被称为通道(Lane),规范允许一个链路由1,2,4,8,12,16,32个通道组成,通道的数量被称为链路宽度即x1,x2,x4,x8,x16,x32。

![图片[1] - PCIe概述一 - 宋马](https://pic.songma.com/blogimg/20251107/17c84cd3fa8246acab8c85435cf5066f.png)

PCIe为什么采用串行模型?速度是多少?

PCIe作为一种串行模型,必须比PCI的并行模型运行的更快才能实现相同的带宽,PCIe可以在2.5GT/s和5.0GT/s甚至在8.0GT/s稳定工作。

PCI的并行模型有什么缺点?为什么并行总线的性能会被限制?

并行总线使用公共时钟,信号在一个时钟边沿输出,并在下一个边沿输入接收器。这个模型的一个问题是信号从发送器到接收器的传输时间,称为飞行时间。飞行时间必须小于时钟周期,否则模型将无法工作,因此缩短时钟周期是具有挑战性的。为了实现这一点,信号线必须更短,负载减少,但最终这变得不切实际。

![图片[2] - PCIe概述一 - 宋马](https://pic.songma.com/blogimg/20251107/fd0758bf35fa4da99f18bb9aac7288a2.png)

PCIe的串行模型如何解决这些问题?

首先,传输延迟不再是问题,因为用于锁存数据到接收端的时钟实际上是内置在数据流中的,无需外部参考时钟。因此,无论时钟周期多短或者信号到达接收端需要多长时间都无关紧要,因为时钟会与数据同时到达。出于同样的原因,不会存在时钟偏移问题,因为锁存时钟是从数据流中恢复的。最后,由于每个通道只发送一个数据位,通道内的信号偏移问题也被消除了。

PCIe的速率

PCIe前两代采用8b/10b编码,即8位输入,10位输出,第三代采用128b/130b编码。比如:PCIe Gen1的物理层链路速率为2.5GT/s,即1秒2.5G次传输,1次传输1个比特,就是2.5Gbps/s。

Gen1 PCIe Bandwidth = (2.5 Gb/s x 2 directions) / 10 bits per symbol = 0.5 GB/s.

Gen2 PCIe Bandwidth = (5.0 Gb/s x 2 directions) / 10 bits per symbol = 1.0 GB/s.

Gen3 PCIe Bandwidth = (8.0 Gb/s x 2 directions) / 8 bits per byte = 2.0 GB/s. //128b/130b损失忽略不计

PCIe没有公共时钟,数据是如何采样的?

PCIe 链路不需要公共时钟,因为它使用源同步模式,这意味着发射端提供时钟给接收端用于锁存接收到的数据。PCIe 链路不包含转发时钟。相反,发射端使用 8b/10b 编码将时钟嵌入数据流中。然后,接收端从数据流中恢复时钟并用它来锁存输入数据。PLL 电路以输入的比特流作为参考时钟,将其时间或相位与其生成的具有指定频率的输出时钟进行比较。根据比较结果,输出时钟的频率会增加或减少,直到匹配为止。此时,PLL 被认为已经锁定,输出(恢复的)时钟频率精确匹配用于传输数据的时钟。注:关于时钟恢复需要注意的一点是,PLL 确实需要输入信号有转换以进行相位比较。如果数据长时间没有转换,PLL 可能会开始偏离正确的频率。为了防止这一问题,8b/10b 编码的设计目标之一是确保在比特流中连续出现 1 或 0 的次数不超过 5 个。

PCIe接收方如何处理收到的比特流?

基于数据包的协议:PCIe 中的所有事务都是以称为数据包的定义结构发送的。接收方查找数据包的边界,并根据预期的模式对数据包结构进行解码,以确定应采取的操作。

PCIe拓扑结构

由于PCIe使用的速度非常高,连接必须是点对点的,而不能像 PCI 那样采用共享总线。因此,由于一个连接只能连接两个接口,需要一种方法来扩展连接。在 PCIe 中,这是通过使用交换机和桥接器来实现的,它们允许在构建系统拓扑(系统中各元素之间的连接集合)时具有灵活性。

Root Complex:CPU 与 PCIe 总线之间的接口可能包含多个组件(处理器接口、DRAM 接口等),甚至可能包含多个芯片。统称为根复合体(Root Complex,简称 RC 或 Root)。根复合体位于 PCI 倒置树型结构的“根”部,并代表 CPU 与系统的其他部分进行通信。规范中并未完全定义它,而是列出了必需和可选的功能。从广义上讲,根复合体可以理解为系统 CPU 与 PCIe 拓扑之间的接口,PCIe 端口在配置空间中标记为“根端口”。比如:RK3588有三个pcie控制器,可以都工作于rc模式,也可以工作于ep模式。Switches and Bridges:交换机提供扇出或聚合功能,并允许更多设备连接到单个 PCIe 端口。它们充当数据包路由器,根据数据包的地址或其他路由信息识别数据包需要经过的路径。桥接器提供与其他总线的接口,例如 PCI 或 PCI‑X,甚至是另一条 PCIe 总线。ep and legacy ep:端点是在 PCIe 拓扑中既不是交换机也不是桥接器的设备,它们在总线上充当事务的发起者和完成者。它们位于树形拓扑的分支底部,并且只实现一个上行端口(朝向根节点)。相比之下,交换机可能有多个下行端口,但只能有一个上行端口。那些最初为旧总线(如 PCI-X)设计但现在具备 PCIe 接口的设备,会在配置寄存器中将自身标识为“传统(legacy) PCIe 端点”,此类拓扑中也包括这类设备。它们会使用在较新 PCIe 设计中被禁止的功能,例如 IO 空间、对 IO 事务的支持或锁定请求。相比之下,“原生 PCIe 端点”是指从零开始设计的 PCIe 设备,而不是在旧 PCI 设备设计上添加 PCIe 接口。原生 PCIe 端点设备是内存映射设备(MMIO 设备)。

Root Complex:CPU 与 PCIe 总线之间的接口可能包含多个组件(处理器接口、DRAM 接口等),甚至可能包含多个芯片。统称为根复合体(Root Complex,简称 RC 或 Root)。根复合体位于 PCI 倒置树型结构的“根”部,并代表 CPU 与系统的其他部分进行通信。规范中并未完全定义它,而是列出了必需和可选的功能。从广义上讲,根复合体可以理解为系统 CPU 与 PCIe 拓扑之间的接口,PCIe 端口在配置空间中标记为“根端口”。比如:RK3588有三个pcie控制器,可以都工作于rc模式,也可以工作于ep模式。Switches and Bridges:交换机提供扇出或聚合功能,并允许更多设备连接到单个 PCIe 端口。它们充当数据包路由器,根据数据包的地址或其他路由信息识别数据包需要经过的路径。桥接器提供与其他总线的接口,例如 PCI 或 PCI‑X,甚至是另一条 PCIe 总线。ep and legacy ep:端点是在 PCIe 拓扑中既不是交换机也不是桥接器的设备,它们在总线上充当事务的发起者和完成者。它们位于树形拓扑的分支底部,并且只实现一个上行端口(朝向根节点)。相比之下,交换机可能有多个下行端口,但只能有一个上行端口。那些最初为旧总线(如 PCI-X)设计但现在具备 PCIe 接口的设备,会在配置寄存器中将自身标识为“传统(legacy) PCIe 端点”,此类拓扑中也包括这类设备。它们会使用在较新 PCIe 设计中被禁止的功能,例如 IO 空间、对 IO 事务的支持或锁定请求。相比之下,“原生 PCIe 端点”是指从零开始设计的 PCIe 设备,而不是在旧 PCI 设备设计上添加 PCIe 接口。原生 PCIe 端点设备是内存映射设备(MMIO 设备)。

PCIe分层架构

设备核心与事务层接口:核心实现设备的主要功能。如果设备是端点,它可能包含多达8个功能,每个功能实现其自己的配置空间。如果设备是交换机,交换机核心包括数据包路由逻辑和用于实现此目标的内部总线。如果设备是根设备,根核心实现一个虚拟的 PCI 总线 0,所有芯片组嵌入的端点和虚拟桥都位于该总线上。事务层:该层负责在发送端创建事务层数据包(TLP),并在接收端对TLP进行解码。该层还负责服务质量功能、流量控制功能和事务排序功能。数据链路层:该层负责在发送端创建数据链路层数据包(DLLP)并在接收端进行解码。该层还负责链路错误检测与纠正。此数据链路层功能被称为确认/否认(Ack/Nak)协议。物理层:该层负责在发送端创建有序集(Ordered‐Set)数据包,并在接收端解码有序集数据包。该层处理在链路上发送的三种数据包类型(TLP、DLLP 和 Ordered‐Sets),并处理从链路接收到的所有类型数据包。

在PCIe拓扑结构中的每个设备是否都支持这些层呢?

每个 PCIe 接口都支持这些层的功能,包括交换端口。

PCIe的各层是如何交互的?

事务层根据设备核心逻辑(也可以叫软件层)提供的信息组装出一个请求或者一个完成数据包。这些信息通常包括所需命令的类型、目标设备地址、请求属性等。当数据包传递到数据链路层(Data Link Layer)时,会向数据包添加额外信息,用于在邻近接收端进行错误检查,并在本地存储一份副本,以便在传输错误时重新发送。当数据包到达物理层(Physical Layer)时,它会被编码并通过链路的所有可用通道进行差分传输。

PCIe的各层详解

1. Device Core / Software Layer

软件层位于事务层之上,并且将成为所有请求的源或目的地。它为事务层的发送端提供请求,其中包含事务类型、地址、传输的数据量等信息。当接收到传入的数据包时,它也是从事务层向上转发信息的目的地。软件层并不会直接封装数据发送,而是OS的PCI子系统/驱动通过访问控制器的寄存器来让硬件生成。从逻辑上看,相当于告诉事务层我要发一个请求(读 / 写 / 配置)到某个设备地址。

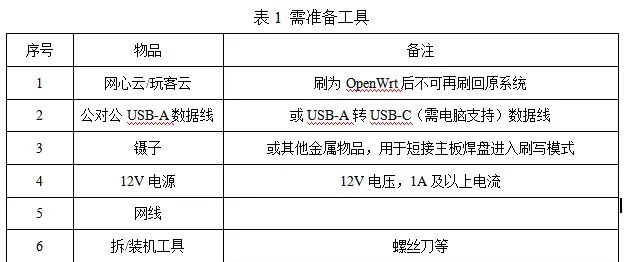

2.Transaction Layer

为了响应来自软件层的请求,事务层生成外发数据包。它还会检查入站数据包,并将其中包含的信息转发到软件层,该层处理的事务使用 TLP(事务层数据包),可分为四类请求:

MemoryIOConfigurationMessages

![图片[3] - PCIe概述一 - 宋马](https://pic.songma.com/blogimg/20251107/bc325f500ee44723898bc121639e38c8.png)

对于non-posted:是指请求者发送一个数据包,完成者生成一个完成数据包响应。内存写入和消息是posted的,这意味着目标设备不会向请求者放回完成的TLP。以下只是简单接收在事务层应该收发什么请求包,具体的包格式以及路由方式以后的文章再说。

2.1 TLP (Transaction Layer Packet) Basics

事务层传输的各种请求数据包以及回复数据包如下图所示:

TLP数据包起源于发送器的事务层,并在接收器的事务层终止,数据链路层和物理层在数据包通过发送器的各层时添加部分内容,然后在接收器验证这些部分是否已正确地通过链路传输。

TLP数据包起源于发送器的事务层,并在接收器的事务层终止,数据链路层和物理层在数据包通过发送器的各层时添加部分内容,然后在接收器验证这些部分是否已正确地通过链路传输。

2.2 TLP (Transaction Layer Packet) Assembly

2.3 TLP (Transaction Layer Packet) Disassembly

2.4 TLP (Transaction Layer Packet) Non-Posted Read

2.4.1. Mrd示例如下图所示:

EP端点发送内存请求包,请求包中含有目标地址,内存请求的地址可以是32位或64位,请求包中字段可以决定数据包的路由。在此示例中,请求通过两个交换机路由,并将其转发到目标(本例中为根端口)。当根端口解码请求并识别数据包中的地址指向系统内存时,它会获取请求的数据。为了将这些数据返回给请求方,根端口的事务层会创建足够多的完成响应,以将所有请求的数据交付给请求方。PCIe 的单个数据包最大数据有效负载为 4 KB,但设备通常设计为使用比这更小的有效负载,因此可能需要多个完成响应来返回大量数据。请求包中有部分字段定义了返回地址,完成包中也包含相同的信息,用于将完成包路由回请求者。返回地址就是请求者的设备ID,通常由三部分组成:系统中的PCI总线号,该总线上的设备号,该设备中的功能号。请求者可以有多个分离的事务正在进行,所以必须区别完成包对应哪个请求,为了便于这一点,原始请求中增加了一个称为标签(Tags)的值,该值在每个请求中都是唯一的。完成者会复制这个事务标签并在完成包中使用它,以便请求者能够快速识别该完成包正在处理哪个请求。

2.4.2. IO和config write示例如下图所示:

IO和配置写入请求只能来自处理器。请求根据 IO 地址经过交换机路由,直到到达目标端点。当完成器收到请求时,它会接收数据并返回一个不含数据的完成包以确认收到该数据包。完成包中的状态字段会报告是否发生错误,如果发生错误,请求方的软件将处理它。如果完成包未报告错误,请求方就知道写入的数据已成功传送,且此完成器的下一条指令现在可以执行。

2.5 TLP (Transaction Layer Packet) Posted Write

Posted的写入包括内存写入和消息写入,这种类型不要求接收者返回完成包。

2.5.1. Mwr示例如下图所示:

数据包通过系统使用其目标内存地址路由到完成者,就是说数据包中携带地址信息,而这个地址信息是某个EP设备特有的,可以通过这个地址信息判断路由路径,从而到达EP端点。一旦某条链路成功发送了请求,该交易在该链路上就完成,并可供其他数据包使用。

2.5.2. Message Write:

消息有几种可能的路由方式,消息内部有一个字段指示使用哪种类型。例如,一些消息是针对特定完成器的写入请求,另一些则是从根节点广播到所有端点,还有一些从端点发送的消息会自动路由到根节点。

3. Data Link Layer

数据链路层负责链路管理,并执行三项主要功能:TLP 错误校正、流量控制以及部分链路电源管理。它通过生成 DLLP 来实现这些功能。DLLP (Data Link Layer Packets)在链路上的两个邻近设备的数据链路层之间传输。事务层甚至不会意识到这些数据包,它们仅在邻近设备之间传输,不会被路由到其他地方。与 TLP 相比,它们很小(始终仅 8 字节)。

DLLP 起源于发送端的数据链路层,并由接收端的数据链路层使用。在 DLLP 核心中添加了一个16位 CRC,用于在接收端检查错误。数据链路层会检查 CRC 错误,然后根据数据包采取适当的操作。数据链路层是 DLLP 的目的地,因此它不会被转发到事务层。

DLLP 起源于发送端的数据链路层,并由接收端的数据链路层使用。在 DLLP 核心中添加了一个16位 CRC,用于在接收端检查错误。数据链路层会检查 CRC 错误,然后根据数据包采取适当的操作。数据链路层是 DLLP 的目的地,因此它不会被转发到事务层。

3.1 Ack/Nak Protocal

数据链路层通过使用Ack/Nak协议来实现错误校正,通过硬件自动重试机制实现。每个发送的TLP都会添加LCRC和序列号,并在接收端进行检查。发送端的重放缓冲区会保留已发送的每个TLP的副本,直到收到邻近设备的确认。该确认以接收端发送的Ack DLLP(正确认)形式出现,包含其已接收到的最后一个有效TLP的序列号。当发送端收到Ack时,它会从重放缓冲区中清除该序列号对应的TLP,以及在该TLP之前发送的所有TLP。如果接收端检测到TLP错误,它会丢弃该TLP并向发送端返回Nak,随后发送端会重放所有未确认的TLP,以期下一次能够成功。

4字节DLLP Type+Misc,2字节CRC,2字节LCRC。

4字节DLLP Type+Misc,2字节CRC,2字节LCRC。

3.2 Flow Control

3.3 Power Management

4. Physical Layer

物理层是 PCIe 的最低层次层,TLP 和 DLLP 类型的数据包都会从数据链路层向下转发到物理层,以便通过链路进行传输,并在接收端向上转发到数据链路层。规范将物理层的讨论分为两部分:逻辑部分和电气部分,我们在这里也将保持这种划分。逻辑物理层包含与准备数据包在链路上进行串行传输及对入站数据包进行反向处理相关的数字逻辑。电气物理层是物理层的模拟接口,它连接到链路,由每条通道的差分驱动器和接收器组成。

数据包的字节会通过一种称为字节条带化的过程分布到链路中使用的所有通道上,其数据在接收端被聚合回一起,每个字节都会进行扰码处理,会把字符经过8b/10b或者128b/130b编码。

数据包的字节会通过一种称为字节条带化的过程分布到链路中使用的所有通道上,其数据在接收端被聚合回一起,每个字节都会进行扰码处理,会把字符经过8b/10b或者128b/130b编码。

4.1 Link Training and Initialization

物理层的另一个职责是链路的初始化和训练过程。在这个全自动过程里,为了让链路进入正常工作状态,需要进行若干步骤,其中涉及确定若干可选条件的状态。例如,链路宽度可以从一条通道到32条通道不等,并且可能存在多种速度选择。训练过程会发现这些选项,并通过状态机序列来确定最佳组合。在此过程中,会检查或建立若干事项以确保正常且最佳的操作,例如:

Link widthLink data rateLane reversal ‐ Lanes connected in reverse orderPolarity inversion ‐ Lane polarity connected backwardBit lock per Lane ‐ Recovering the transmitter clockSymbol lock per Lane ‐ Finding a recognizable position in the bit‐streamLane‐to‐Lane de‐skew within a multi‐Lane Link

4.2 Physical Layer – Electrical

链路上的物理发送器和接收器通过AC耦合链路连接。“AC耦合”一词简单地意味着在设备之间的路径中物理上存在一个电容器,它用于传递信号的高频(交流)分量,同时阻断低频(直流)部分。许多串行传输使用这种方法,因为它允许发送端和接收端的共模电压(即信号正负版本交叉的电平)不同,这意味着它们无需具有相同的参考电压。

PCIe传输示例

Memory Read Request:

![图片[4] - PCIe概述一 - 宋马](https://pic.songma.com/blogimg/20251107/5a8ff711feed412b9ce3e3482ee5716c.png)

请求方的设备核心或软件层向事务层发送请求,并包括以下信息:32位或64位内存地址、事务类型、以双字为单位计算的数据读取量、流量类别、字节使能、属性等。事务层使用这些信息来构建 MRd TLP,根据地址大小(32 位或 64 位),会创建 3 DW 或 4 DW 的头部。此外,事务层会在头部添加请求者 ID(总线号、设备号、功能号),以便完成器用于返回完成。TLP 会被放置在相应的虚拟通道缓冲区中,等待其传输的顺序。一旦 TLP 被选中,流量控制逻辑会确认相邻设备的接收缓冲区(VC)中有足够空间,然后内存读取请求 TLP 会被发送到数据链路层。数据链路层为数据包添加一个12位的序列号和一个32位的LCRC值。带有序列号和LCRC的TLP副本存储在重播缓冲区中,并将数据包转发到物理层。在物理层中,开始和结束字符被添加到数据包中,然后数据包被按字节分布到可用的通道上,进行扰码处理,并进行8b/10b编码。最后,各通道上的比特被串行化,并通过差分方式在链路上传输到邻居设备。完成器将传入的比特流反序列化回10位符号,并将其传递通过弹性缓冲区。10位符号被解码回字节,并且来自所有通道的字节被去扰码和重排。起始和结束字符被检测并移除。剩余的TLP被转发到数据链路层。完成者的数据链路层会检查接收的 TLP 中的 LCRC 错误,并检查序列号以确认是否有缺失或顺序错误的 TLP。如果没有错误,它会创建一个包含在读取请求中使用的相同序列号的确认信息 (Ack)。随后计算一个 16 位 CRC 并附加到 Ack 内容中,以生成一个 DLLP,该 DLLP 会被发送回物理层,物理层会添加适当的帧符号并将 Ack DLLP 传送给请求者。请求方物理层接收 Ack DLLP,检查并移除帧符号,然后将其转发至数据链路层。如果 CRC 有效,它会将被确认的序列号与存储在重放缓冲区中的 TLP 序列号进行比较。与收到的 Ack 相关的存储的内存读取请求 TLP 会被识别,并从重放缓冲区中丢弃。如果请求方收到的是 Nak DLLP,它将重新发送存储的内存读取请求 TLP 的副本。由于 DLLP 仅对数据链路层有意义,因此不会将任何内容转发到事务层。除了生成确认(Ack)之外,完成端的链路层还会将事务层包(TLP)向其事务层转发。在完成端的事务层中,TLP会被放置在相应的虚拟通道接收缓冲区中进行处理。可以选择执行可选的ECRC检查,如果未发现错误,报文头的内容(地址、请求者ID、内存读取事务类型、请求的数据量、流量类别等)将被转发到完成端的软件层。

Completion with Data:

![图片[5] - PCIe概述一 - 宋马](https://pic.songma.com/blogimg/20251107/7f352354806e4df9af16310ebba95423.png)

为响应内存读取请求,完成设备核心/软件层向其事务层发送带数据的完成(CplD)请求,该请求包含从原始内存读取请求复制的请求者ID和标签、事务类型、完成报头的其他部分内容以及所请求的数据。事务层使用这些信息来构建 CplD TLP,它始终具有 3 DW 的头部(它使用 ID 路由,并且从不需要 64 位地址)。它还将自己的完成器 ID 添加到头部。该数据包还会被放入相应的虚拟通道发送缓冲区,一旦被选择,流量控制逻辑会验证相邻设备是否有足够的空间接收此数据包,一旦确认,就将数据包传送到数据链路层。和以前一样,数据链路层会在数据包中添加一个12位的序列号和一个32位的LCRC。带有序列号和LCRC的TLP副本会存储在重传缓冲区中,数据包随后被转发到物理层。与之前一样,物理层在数据包中添加起始和结束字符,将其按字节分配到可用通道上,对其进行扰码处理,然后进行8b/10b编码。最后,CplD数据包在所有通道上进行串行化,并以差分方式通过链路传输到邻节点。请求方将接收到的串行比特流转换回10位符号,并将其传递通过弹性缓冲区。这些10位符号被解码回字节,去扰码并去条带化。检测并移除起始和结束字符后,将得到的TLP发送到数据链路层。与之前一样,数据链路层会检查接收到的 CplD TLP 中的 LCRC 错误,并检查序列号是否有丢失或乱序的 TLP。如果没有错误,它会创建一个 Ack DLLP,其中包含与所用 CplD TLP 相同的序列号。然后在 Ack DLLP 上添加 16 位 CRC,并将其发送回物理层,物理层会添加适当的帧符号并将 Ack DLLP 传输给完成者。完成者物理层检查并移除来自确认 DLLP 的帧符号,然后将其余部分发送到数据链路层,数据链路层会检查 CRC。如果没有错误,它会将序列号与重放缓冲区中存储的 TLP 的序列号进行比较。与收到的确认相关的存储的 CplD TLP 会被识别,并且该 TLP 会从重放缓冲区中丢弃。如果完成者收到的是否定确认 DLLP,它将重新发送存储的 CplD TLP 的副本。与此同时,请求者事务层在相应的虚拟通道缓冲区接收CplD TLP。可选地,事务层可以检查ECRC错误。如果没有错误,它会将头部内容和数据负载(包括完成状态)转发给请求者软件层,然后完成处理。

暂无评论内容