一、仿真接口包含哪些信号,信号数据速率、信号方向,仿真完成后查看什么位置的波形(谁用这个信号就看谁的,也就是input端)

![图片[1] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/bf4bcd6bca9d4b2980d658dee82d4fd3.jpeg)

比如:TI的574x的技术手册,其中,在读数据时,有一个rtclk,它控制数据的读操作。

信号的方向,如上图。

至于数据速率,也从手册上找

![图片[2] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/c37919e50e1b4b0cbcae4d98ae871ac5.jpeg)

这里有几种工作模式,对于硬件设计来说,要选频率最高的,也就是10.41ns,约为96MHz。

二、仿真准备

搜集ibis模型,使用TI的开发板为参考,查找am574x.ibs,flash的ibs模型有很多,从中筛选出合适的

![图片[3] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/dc592665bbc642388336456e47357446.jpeg)

第一个条件,使用的是3.3V器件,原理图的芯片型号S25FL256SAGMFIR01,温度等级是I,85度,所以选85C_33V的;

![图片[4] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/23f4ca6905d34f8b96437b83f5fa7bc3.jpeg)

中间的bckmw代表不同的封装,这里用的16PIN SOIC封装,代号是m,所以选用s25fl256s_m_i_33_r1.ibs

三、打开仿真软件SPEEDEM Generator

![图片[5] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/a2a1630ea1b74624ad02fd58b3b693f9.jpeg)

选择左下部分的General SI Simulation(Ideal P/G)

Load Layout File

选用这个,是因为QSPI部分的信号线有完整的参考地平面,可以当成理想的地,这种模式就是不考虑地平面的影响。

使能QSPI相关的信号,包括DGND、V3_3D.

加载ibis模型Assign Component models

![图片[6] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/60efc52fac384b30871bedfc6cb20979.jpeg)

选中U1,Edit Model

![图片[7] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/8b29ce115f9c4c82b0d5c75cdca9a179.jpeg)

![图片[8] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/cf123f0ebf034fbba4d47267a9166f1d.jpeg)

添加之前搜集的ibs文件,确定

对于QSPI芯片U4,同样添加ibs文件。注意Component栏,选择后缀AX,这是因为所选器件S25FL256SAGMFIR01,

![图片[9] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/ab23ec3caae149d88b07636c3ea0ac47.jpeg)

描述中是有Reset和VIO引脚的,而ibis模型里面只有_AX后缀的有这两个引脚。

![图片[10] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/6f5a02a8cffa45c8befeb8d1fd369087.jpeg)

注意勾选左下角的Pin RLC。

![图片[11] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/c36dbddc095946b0979e1198ec93dc23.jpeg)

检查一下,信号中间的电阻,原理图是0欧姆,在仿真模型中是否也是0欧姆

![图片[12] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/131ed856215445f6935510f5b5f1530d.jpeg)

R22和R799是10K。

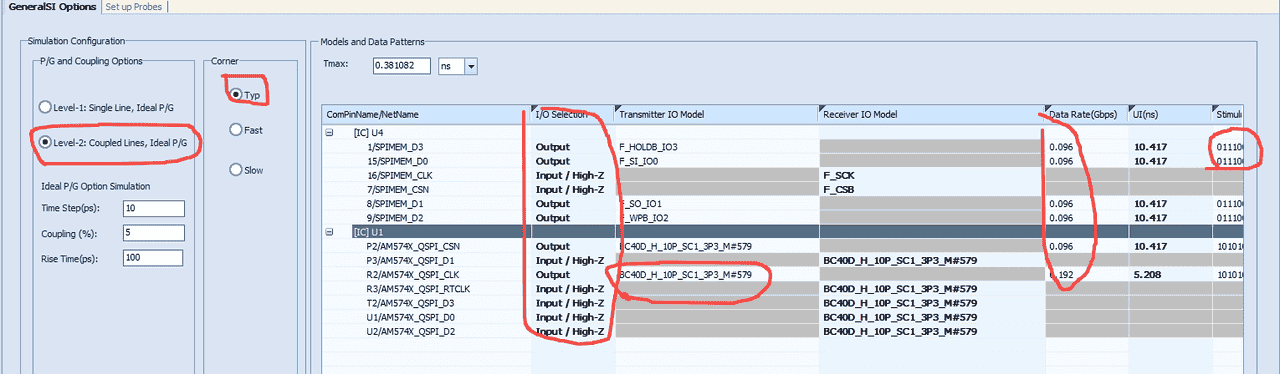

四、仿真设置

从左到右,依次是需要考虑线间的耦合,仿真典型corner,IO的输入输出按照CPU读取Flash的场景仿真,IO模型的选择上Flash只有一种而CPU有很多,选取一个慢速的3P3是3.3V的模型,数据速率按照手册上的最大速率96Mbps,这里单位是Gbps,但是对于时钟信号每个周期是两个bit,算成bps要翻倍;激励数据波形至少采用PRBS5_含补码的01110010001010111101101001100001000110111010100001001011001111,时钟和CSN信号就用01010101的数据就行了,注意数据末尾的两个点…表示数据重复,不要丢掉了。仿真时间至少覆盖一个完成的62bit,一个UI是10.4,设置稍大一点800ns。完整设置如下,时间未改,按自己喜好改:

探针选择,这里按默认全部采集

![图片[13] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/09c3e22f2821474d888872a4830e5cfe.jpeg)

OK了,保存,仿真

如果出现

ERROR [Node Placement]: Via10635::DGND at (65.119mm, 110.136mm) with lower node on Signal_S3_SIG1 has a placement error

这种类型的错误导致无法仿真,试试修改设置

查看波形,左侧出现两个波形类型,die和pin,对应封装内部die上的pad和封装外部的引脚上的波形,在这里,我们最关心的是die上的波形,这才是输入到芯片的信号质量,但是这个信号是无法实际测量的。在检验仿测是否一致的时候,还是只能用pin的波形与实际测量的波形进行对比。

在这里,只有仿真,所以更关心die上的波形。

波形首先要满足电气特性,就是过冲,芯片手册上有过冲和下冲的最大值和最大持续时间的要求。超过会烧毁元器件引脚的mos管。手册要求20%,所以最大值3.3*1.2=3.96V,下冲-0.66V,波形上右键Marker,添加3.96V和-0.66V两条水平的标线,

![图片[14] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/8ba1229ffa9548d8b22fcf253949c794.jpeg)

![图片[15] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/91600269cd0b413391cbca3b4dcfc46a.jpeg)

每个信号都检查一遍,是否在标线范围之内。Flash芯片要求过冲下冲不超过标准值再加2V,这个更没有问题了。

信号质量是否满足要求?

对于数据、地址信号,都是电平有效信号,注意高低电平的门限及时间窗口是否满足要求,波形上的回调,如果超过了门限值,会严重缩短信号的时间窗口。

这里芯片要求的高低门限值是0.8V和2V,添加这两个标线

![图片[16] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/a169787f7e87471b8e39c8d523d40222.jpeg)

![图片[17] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/25f951f971a14387a34cd1a283206e65.jpeg)

回调不能超过门限,指的就是低电平的高峰和高电平的低峰不能超过这个门限值。

这种仿真并没有考虑板上其它噪声对信号的影响,所以实际波形应该更差,所以仿真的结果临近门限时就相当危险了。

对于时钟等边沿有效信号,需要考虑其边沿的单调性。对于本次芯片,它的时钟信号的门限也是0.8V和2V。

![图片[18] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/d11c491d92924197b3ddb0f7cdea7c82.jpeg)

![图片[19] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/ea6eaef390e4430f84156eadffa2a302.jpeg)

它的边沿单调性指的就是在两个门限值之间的时候不能有上下的震荡。

有的可能对上升时间有要求。

对于信号的优化,使用HyperLynx比较快捷。

五,HyperLynx导入Cadence的brd文件

用Allegro打开brd,export输出ODB++,如果没有这个选项就需要安装ODB++插件。

![图片[20] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/59b920ad05d3400ca067ecb4f32403aa.jpeg)

这里需要输出压缩包.tgz

打开HyperLynx,打开刚才输出的文件

![图片[21] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/4d2216d6912748f38b5f85b1bd785ebc.jpeg)

在信号上右键,使能数据线D1的net

![图片[22] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/768d3c54c304461691d5d01ffa3154d2.jpeg)

也可以菜单栏Select-Net by Name for SI Analysis…

![图片[23] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/ae0ecd26b0cc4627975a274ac28465a9.jpeg)

添加ibis模型路径,Models-添加模型库路径,把自己的文件夹添加进去。

![图片[24] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/9de0ccd28a144de2bb49ea23136aa2da.jpeg)

models-assign models

![图片[25] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/b98d6cbdaa7847c98e8d510b769ec7da.jpeg)

![图片[26] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/2778a8f5407640a6931f051a89f13ece.jpeg)

注意,这里选择的时GPMC_A17,因为这是复用引脚,可以看原理图.同时,注意模型选择器,不要选错了,应该与之前一样,选择后尾是579的那个IO模型。

![图片[27] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/7048a9e7be6349b09fa36f6cc61054c5.jpeg)

信号D1对应的引脚其实是GPMC_A17。

对于Flash芯片的引脚,和之前的选择一样,尾缀AX,引脚名称SO/IO1.

![图片[28] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/f75bc09eb7a64e05b497dec12996473f.jpeg)

电阻,赋值,0欧姆.确定,设置信号方向,U4为Output U1为Input。

导出到原理图

Export-Net To-Free-Form Schematic…不用勾选其它选项

![图片[29] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/5a532e18339f484cabf9a4313e1e4e14.jpeg)

![图片[30] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/40528093d7984f5690fe7a19f106a878.jpeg)

运行交互式仿真

![图片[31] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/c41a1ca8472a49c69058b195b20aa377.png)

![图片[32] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/f45ff1d35ab948d5b46135c57ef1962a.png)

选择R26,add Range添加扫描范围和步长,这里设置0-40欧姆,步长10欧姆

![图片[33] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/59575f097f6546d49459eb5102b92adc.jpeg)

点运行扫描

![图片[34] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/6e78b2357265498eb0317951398c6543.jpeg)

运行扫描,调整刻度

![图片[35] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/9d30ea66df8d4dccb6ed9384d7baeb0d.jpeg)

![图片[36] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/432fd505f9f443d394a63b982ea0354f.jpeg)

对比0欧、10欧、20欧的波形,发现10欧的最好。

也可以选择查看die上的波形

![图片[37] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/fb015b2924a044fb81c4f86324d1e05c.png)

对于时钟信号的优化,同样,选取网络,赋模型

![图片[38] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/495f28303fd84f4db9cf18e412dea8a8.jpeg)

R2是输出,另外两个是输入,电阻同样都是0欧姆。

同样,export出自由形态原理图。

![图片[39] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/df74272723464825b30d17503e431f57.jpeg)

先看R24对波形的影响

![图片[40] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/579d0b2958fa4aad85886d629e6ed832.jpeg)

阻值增大,波形变缓。

![图片[41] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/0947317509c54a5bba87c835b6fab34c.jpeg)

对于R23和R31,如果想让它们同步变化,可以设置粘贴范围并锁定。

![图片[42] - QSPI的SI仿真 - 宋马](https://pic.songma.com/blogimg/20251120/aae5a427e5c74405a3b2627830f5e5e3.jpeg)

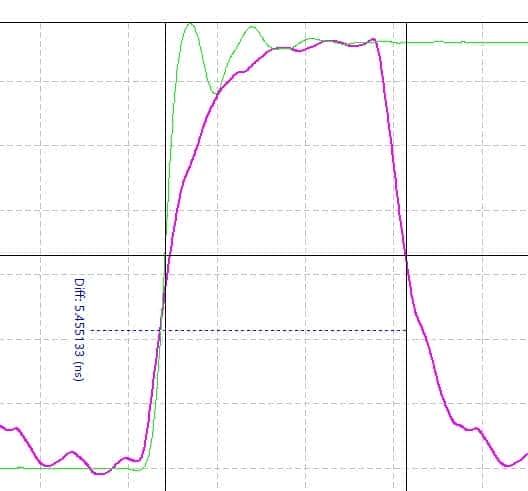

对于建立时间的测量,可以直接在波形上使用maker和measure来测量,如下图,可以看到差值是5.4ns。

暂无评论内容