系列文章目录

第一章 Uefi Gpio配置原理

第二章 总结

文章目录

系列文章目录前言第一章 Uefi Gpio配置原理第二章、总结

前言

前面介绍了整体的Bring Up需要事项,本文中主要深入的介绍BU过程中GPIO合入配置。

第一章 Uefi Gpio配置原理

配置GPIO首先需要配置客户提供的gpio pin和function的对接。这里例举某项目的GPIO Table:

#GPIO

BE4 GPIO151/PM_GPIO0 1.8V S0 Push-Pull Pull Up PMIC0_I2C_INT_L input Reserved,PMIC0 Interrupt event to alert SOC; Low active

BE5 GPIO152/PM_GPIO1 1.8V S0 Push-Pull Pull Up PMIC1_I2C_INT_L input Reserved,PMIC1 Interrupt event to alert SOC; Low active

BF4 GPIO153/PM_GPIO2 1.8V S0 Push-Pull Pull Up GPIO153/PM_GPIO2

#SSD

T4 GPIO004 1.8V S5 Push-Pull Pull Down M2_NVME_RST_L output To reset PCIe devices; SSD

#LAN

W8 GPIO005 1.8V S5 Push-Pull Pull Down ETH_PWR_CTL output RTL8111HS Power Enable

T5 GPIO006 1.8V S5 Push-Pull Pull Down LOM_RST_L output PCIE LAN“PERST#” signal, Low Active

在GPIO_CFG结构体中有5个参数,参数意义如下:

| 参数 | 描述 |

|---|---|

| NUM | GPIO的序号(1为最小GPIO 序号) |

| Direction | GPIO配置输入、输出的选择 |

| OutputVal | 当GPIO配置成输出时,GPIO所输出的电平值 |

| IntrEn | GPIO中断的使能,1为使能 |

| IntrType | GPIO中断触发方式的选择 |

typedef struct _GPIO_CFG {

UINT32 Num;

IO_DIRECTION_SEL Direction;

IO_INOUT_VALUE_SEL OutputVal;

IO_INTERRUPT_ENABLE_SEL IntrEn;

IO_INTERRUPT_TYPE_SEL IntrType;

} GPIO_CFG;

GpioCfgTable中所需要的配置值均封装为宏定义,也可在头文件中查看或引用。

GPIO_CFG结构体中的Num 为以1为最小定义的GPIO序号的立即数定义GPIO_CFG结构体中的Direction域对应头文件中IO_DIRECTION_SEL枚举定义GPIO_CFG结构体中的OutputVal域对应头文件中以IO_INOUT_VALUE_SEL枚举定义GPIO_CFG结构体中的IntrEn域对应头文件中IO_INTERRUPT_ENABLE_SEL枚举定义GPIO_CFG结构体中的IntrType域对应头文件中IO_INTERRUPT_TYPE_SEL枚举定义

本平台支持5个PCIE Port,配置如下表:

| Item | Port0 | Port1 | Port2 | Port3 | Port4 |

|---|---|---|---|---|---|

| Highest Generation | Gen4 | Gen4 | Gen4 | Gen4 | Gen4 |

| Max Lane Number | 8 | 4 | 2 | 1 | 1 |

| Reference Type | GPU | NVMe | WWAN | WIFI | Ethernet |

每个PCIE Port的开关配置如下[TRUE: Enable, FALSE: Disable]每个PCIE Port的Lane Number配置如下[0x00:X1, 0x01:X2, 0x02:X4, 0x03:X8]每个PCIE Port的Link Speed配置如下[0x01: GEN1, 0x02: GEN2, 0x03: GEN3, 0x04: GEN4]每个PCIE Port的Max Speed配置如下[0x00: GEN1, 0x01: GEN2, 0x02: GEN3, 0x03: GEN4]每个PCIE Port的Max ASPM Capability配置如下[0x00: Disable, 0x01: L0s, 0x02: L1, 0x03 L0sL1]每个PCIE Port的ASPM配置如下[0x00: Disable, 0x01: L0s, 0x02: L1, 0x03 L0sL1]每个PCIE Port的Max Payload配置如下[0x00: 128bytes, 0x01: 256bytes, 0x02: 512bytes]每个PCIE Port对应Reset GPIO Pin配置如下[0x00: None, 0x01: GPIO01 0x02: GPIO02…]

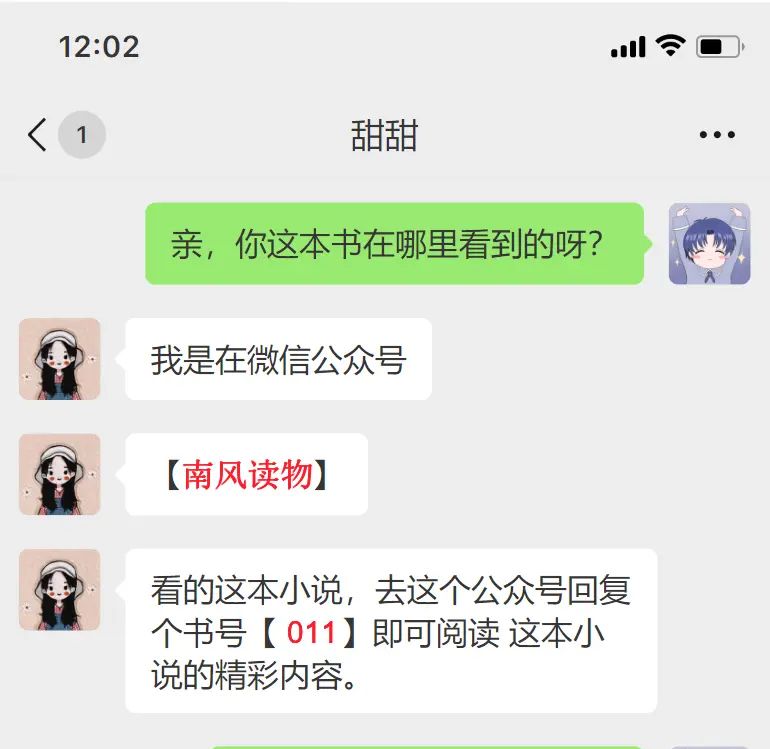

针对次特性,Edge项目需要在Platform/CIX/Sky1/Edge/Edge.dsc中配置Pcie gpio

![图片[1] - Edge server项目Bring up系列文章(二) - 宋马](https://pic.songma.com/blogimg/20251123/d592a27045e5498eb8502e7c01bc67eb.png)

这里配置了nvme和ethernet的gpio reset pin,配置的逻辑:

按照Lane Numer : x4 = port1

x1 = port 3/4

原理图里SSD GPIO004 = reset pin

LAN GPIO006 = reset pin

所以:

gpio port1是ssd的reset pin,应该是GPIO 4

gCixTokenSpaceGuid.PcdPcieRootPort1PeResetPin|4

gpio port4是lan的reset pin,应该是GPIO 6

gCixTokenSpaceGuid.PcdPcieRootPort4PeResetPin|5

对应的GPIO_CFG GpioCfgTable[] 所需要了解的内容如下:

在本参考平台上,GPIO初始化代码已经被包入了 GPIO 初始化配置结构体中,参考代码在edk2-platforms/Platform/CIX/Sky1/Merak/Library/GpioTableLib/GpioTableLib.c

GPIO_CFG GpioCfgTable[] = {

{ 1, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_DISABLE, EDGE_LOW }, // EC_HID_INT_L

{ 2, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // SLT_X8_RST_L

{ 3, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // SLT_X4_RST_L/M2_WWAN_RST_L

{ 4, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // M2_NVME_RST_L

{ 5, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // M2_WLAN_RST_L

{ 6, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // LOM_RST_L

{ 7, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_DISABLE, EDGE_LOW }, // EC_ACPI_INT_L

{ 8, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_DISABLE, LEVEL_LOW }, // I2C_INT_CPU_PD1

{ 9, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_DISABLE, LEVEL_LOW }, // I2C_INT_CPU_PD2

{ 10, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, LEVEL_LOW }, // TPAD_INT_L

{ 11, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, LEVEL_LOW }, // RTC_ALARM_L

{ 12, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // M2_SSD_PWREN

{ 13, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // WLAN_PWREN

{ 14, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, LEVEL_LOW }, // HP_MIC_DET#/EP_X8_RST_L

{ 30, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // LOM_PEWAKE_L

{ 31, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // SLT_X8_PEWAKE_L

{ 32, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // WLAN_WAKE_L

{ 33, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // SLT_X4_PEWAKE_L

{ 40, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // UART_WAKE#_M2_SOC

{ 43, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // GMAC0_PHY_RESET_L

{ 44, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // GMAC1_PHY_RESET_L

{ 45, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, LEVEL_LOW }, // GMAC0_INT_L

{ 46, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, LEVEL_LOW }, // GMAC1_INT_L

{ 81, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // IR_EN

{ 82, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM2_PWDN

{ 83, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM2_PWREN

{ 84, INPUT, INOUT_VALUE_DEFAULT, INTERRUPT_ENABLE_DEFAULT, LEVEL_LOW }, // TPM_INT_L

{ 85, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM2_RST_L

{ 86, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM3_PWREN

{ 87, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM0_RST_L

{ 88, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM3_RST_L

{ 89, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM3_PWDN

{ 90, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM0_PWDN

{ 91, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM0_PWREN

{ 92, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM1_RST_L

{ 93, OUTPUT, INOUT_LOW, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM1_PWREN

{ 94, OUTPUT, INOUT_HIGH, INTERRUPT_ENABLE_DEFAULT, INTERRUPT_TYPE_DEFAULT }, // CAM1_PWDN

在文件“GpioTableLib.c”里结构体GpioCfgTable是GPIO 初始化配置表。

按照客户原理图中提供的信息:

GPIO006 Push-Pull Pull Down LOM_RST_L output PCIE LAN“PERST#” signal, Low Active

gpio6 是控制power的,需要配置 INOUT_HIGH

第二章、总结

到这里gpio config和客户的特性以及对齐,接下来的章节,会配置DDR相关的配置,编译Bios在runtime debug系统启动情况。

暂无评论内容