最后发现,所谓的“简单”只是被包装好的表象。当项目一复杂起来,STM32的开发变成了在一层层抽象里找底层细节的活——从高层API一路剥开,直到寄存器和参考手册那页页小字。

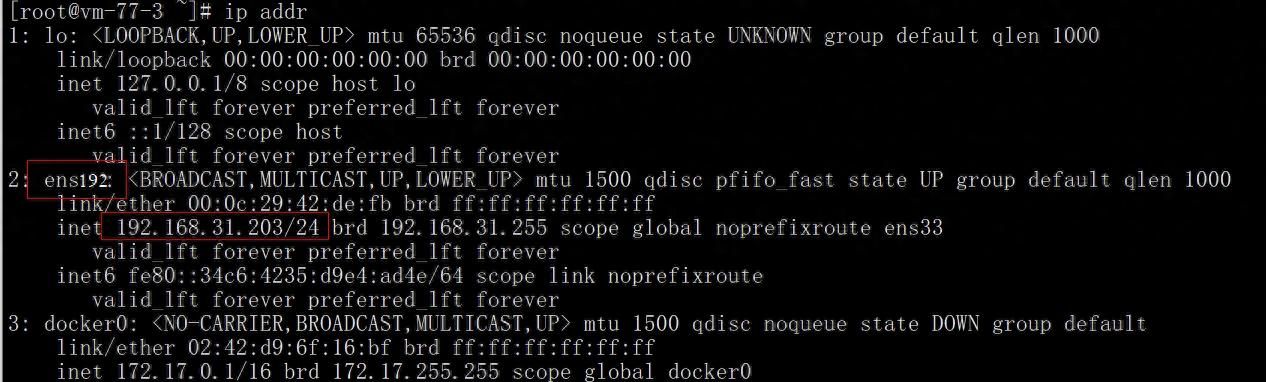

那天的问题是这样开始的:用CubeMX一键生成了初始化代码,按理说外设都弄好了。串口能收发,DMA看着也启动了,但系统一忙起来,串口丢包、DMA停住、偶尔还出现莫名的中断延迟。表面上是几个函数调用,实际却得把应用层一路往下追,把HAL库的实现、库版本差异、参考手册中的寄存器位,都翻一遍才有眉目。最后才发现:某个中断标志没有被软件手动清除,某个时钟分频并没有按照CubeMX显示的那样生效,DMA的一个状态位在特定条件下会卡住不动。

回溯来看,最开始接触STM32的时候,感觉很好用。HAL把许多工作封装了,CubeMX直接生成初始化代码,外设看着像模块化积木:开个串口,调用HAL_UART_Receive,搞定。项目要求用STM32去驱动一块串口智能屏,整合了显示、触摸和多个传感器接口,表面上逻辑不算复杂。但随着功能堆叠,里头的依赖关系开始暴露。中断优先级要细调,DMA和中断之间需要协同,时钟树的一个小偏差会影响外设的波特率和定时行为。

中间的几个转折点挺关键。第一个是当DMA传输出现不稳定时,我们以为是应用层函数用法问题,结果把调试范围一路缩到HAL实现。那时不得不去看源码——一些HAL函数在处理完中断后并没有清理全部标志,倘若你的应用又在别处检查同样的状态,就会产生竞态。第二个转折是时钟问题:CubeMX的图形界面给出了配置,但实际站到芯片上测量时,某处分频并没有按预期工作,导致外围外设的定时误差,很难察觉。第三个是中断优先级和系统中后台任务的干扰。中断响应慢,有时并不是你的回调函数写得慢,而是中间层的调度、系统服务或是库函数里那些看不见的锁在抢占时间片。

把事情往前再推,就是对比FPGA的那段思路。用FPGA时,你写的是硬件描述,信号什么时候变、每拍时钟谁控制,都在你手里。就算是调用IP核,你也能查到它的硬件描述,知道时序走向。那种从逻辑到物理的直接对应让调试变得可预见。在STM32的世界,问题一般出在中间层:API、库版本、文档的勘误表、社区里别人的经验贴。你当然可以只关心高层函数,但当系统复杂起来,这些中间层就像雾霾,把问题的根源遮住了。不得不承认,这份“便捷”一方面省时间,另一方面也把控制权交出了大半。

具体调试细节并不简单。为了解决DMA卡死的情况,先是把外围的配置反复比对,确认描述符、缓冲地址都没问题。接着用示波器抓串口线,确认物理信号有没有丢帧。最后才在HAL的中断处理处发现:某个条件分支在特定循环里没有走到清除状态。修复后,系统稳定性提升明显。处理中断优先级时,问题更容易被忽略——默认优先级看起来合理,但在多中断并发时,会出现低优先级中断被高优先级打断导致关键区域超时的情况。调整NVIC优先级和禁用中断保护关键段,是不得不做的功课。

还遇到过库版本引起的怪癖。一版HAL在某个平台上表现正常,换到另一版库或另一个SDK,初始化顺序稍有变化,外设就表现不同。查对ChangeLog和社区帖子成了常态,许多时候是别人踩过的坑,帖子里有人留下了临时绕过的方法。对照参考手册才发现,有些寄存器位在不同的芯片版本上默认值并不一致,官方文档的勘误表里也藏着必须手动设置的提议。

这些经历带来一个现实感受:STM32不是硬件严苛地把你卡住,而是软件生态给你构建了一个看似完整但不完全透明的环境。你以为自己是在设计逻辑,实际上许多决定已经被抽象层替你做了,你要么接受它带来的限制,要么把抽象一层层剥掉,重新掌控底层。剥开抽象需要时间和耐心,也需要在应用层和寄存器层之间不断切换视角。

在实际项目里,这种切换很频繁。白天在应用层拉取数据,调接口;晚上翻参考手册,对照寄存器位;周末在论坛里搜索类似问题。每次当你以为问题解决了,总会有下一个边缘情况出现,让你意识到系统还没真正被掌握。这样一来,所谓的“简单”就变成了另一种工作模式的折衷:省去一次次重复造轮子的时间,但付出的是更多和抽象层打交道的时间。

- 最新

- 最热

只看作者