第一章:GPU并行计算的黎明:为何选择CUDA与Python?

1.1 计算的瓶颈:从CPU的极限到并行计算的呼唤

自集成电路问世以来,计算能力的提升在很大程度上遵循着戈登·摩尔(Gordon Moore)提出的摩尔定律——集成电路上可容纳的晶体管数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。这一经验性的观察在过去半个多世纪里,奇迹般地指引着半导体产业的发展方向,也使得CPU的性能以惊人的速度迭代。我们经历了从单核到多核,从MHz到GHz的时钟频率飙升,CPU架构也变得日益复杂,通过引入更深的流水线、更强大的分支预测单元、更大的高速缓存、以及更精巧的指令级并行技术(如SIMD指令集SSE, AVX等),不断压榨着串行程序的执行效率。

然而,大约从21世纪初开始,这种单纯依靠提升CPU核心频率和复杂度的发展模式逐渐显露出疲态。几个难以逾越的“墙”开始阻碍CPU性能的持续高速增长:

1.1.1 功耗墙 (The Power Wall)

晶体管的开关需要消耗能量,并且会产生热量。当CPU的时钟频率越高,单位时间内晶体管开关的次数越多,其功耗就越大,产生的热量也越多。根据Dennard缩放定律(Dennard Scaling),在理想情况下,当晶体管尺寸按比例缩小时,其工作电压和电流也应按比例降低,从而使得单位面积的功耗保持不变。但在晶体管尺寸进入纳米级别后,漏电流(leakage current)等问题变得日益严重,Dennard缩放定律逐渐失效。这意味着即使晶体管做得更小,其功耗也难以按比例降低。

为了追求更高的主频,CPU厂商不得不采用更高的电压,这导致功耗呈指数级增长(功耗与频率成正比,与电压的平方成正比,即 (P propto fV^2))。巨大的功耗带来了几个严峻的问题:

散热挑战:CPU产生的热量如果不能及时有效地散发出去,会导致芯片温度过高,影响其稳定运行,甚至永久性损坏。这使得CPU散热系统的设计变得越来越复杂和昂贵,尤其是在移动设备和高密度数据中心中。我们看到CPU从被动散热到风冷,再到高端系统中的水冷甚至更极端的散热方案,都是为了应对这堵“功耗墙”。

能源消耗:高功耗意味着高能源消耗。对于个人用户而言,这可能只是电费的增加;但对于拥有成千上万台服务器的数据中心而言,能源成本和碳排放成为了一个巨大的经济和环境负担。

物理极限:材料的散热能力和电子迁移等物理现象也限制了芯片能承受的最高温度和电流密度。

1.1.2 指令级并行性的极限 (The Instruction-Level Parallelism – ILP Wall)

为了在单个核心内提高执行效率,现代CPU架构师们发明了许多精巧的技术来挖掘指令流中潜在的并行性,统称为指令级并行(ILP)。主要技术包括:

流水线 (Pipelining):将一条指令的执行过程分解成多个阶段(如取指、译码、执行、访存、写回),让不同指令的不同阶段可以重叠执行,类似于工厂的流水线作业。

超标量 (Superscalar):在一个时钟周期内,CPU可以同时发射和执行多条指令。这需要CPU内部有多套执行单元(如整数运算单元、浮点运算单元、加载/存储单元)。

乱序执行 (Out-of-Order Execution, OoOE):CPU可以不按照程序代码的顺序来执行指令。如果后面的某条指令不依赖于前面尚未完成的指令,并且其所需的操作数已经就绪,CPU就可以提前执行它,以避免不必要的等待,提高执行单元的利用率。

寄存器重命名 (Register Renaming):通过为内部物理寄存器动态分配给程序可见的逻辑寄存器,消除由于寄存器名相同而导致的数据伪相关(写后读、写后写冲突),从而为乱序执行创造更多机会。

分支预测 (Branch Prediction):程序中充满了条件分支指令(if-else, loops)。CPU会猜测分支的走向,并提前执行预测路径上的指令。如果预测正确,可以节省大量时间;如果预测错误,则需要回滚已执行的指令,造成性能损失。现代CPU的分支预测准确率已经非常高。

推测执行 (Speculative Execution):结合分支预测,CPU会沿着预测的路径预先执行指令。

这些ILP技术极大地提升了单个CPU核心的性能。然而,程序中固有的数据依赖关系和控制依赖关系限制了可被并行执行的指令数量。研究表明(例如著名的“Patterson and Hennessy”的计算机体系结构教科书中的论述),在典型的非数值计算程序中,平均可并发执行的指令数量通常只有2到4条左右,即使是最激进的ILP技术也难以突破这个瓶颈太多。继续增加CPU核心的复杂度(例如,更多的执行单元、更复杂的乱序逻辑)来挖掘更多的ILP,其带来的性能提升与增加的晶体管数量、设计复杂度和功耗不成正比,即所谓的“收益递减”。这就是指令级并行性极限。

1.1.3 内存墙 (The Memory Wall)

CPU的计算速度与内存(DRAM)的访问速度之间存在着巨大的鸿沟。CPU执行一条指令可能只需要纳秒甚至皮秒级别的时间,而从主内存中读取一个数据则可能需要几十甚至上百纳秒。这种速度差异被称为“内存墙”。

为了缓解内存墙问题,计算机体系结构中引入了多级高速缓存(Cache):L1 Cache, L2 Cache, 甚至L3 Cache。Cache是位于CPU和主内存之间的小容量、高速度的SRAM存储器。它利用了程序访问的局部性原理:

时间局部性 (Temporal Locality):如果一个数据项被访问,那么它在不久的将来很可能再次被访问。

空间局部性 (Spatial Locality):如果一个数据项被访问,那么与它相邻的数据项也很可能很快被访问。

当CPU需要数据时,它首先检查L1 Cache;如果未命中(Cache Miss),则检查L2 Cache,以此类推。如果所有Cache都未命中,才需要从主内存中读取。Cache的命中率越高,CPU等待内存的时间就越少。

尽管Cache技术非常有效,但对于那些需要处理海量数据、并且数据访问模式不规则(局部性差)的应用(例如,大规模图计算、某些数据库操作、以及许多科学计算问题),Cache的效率会大打折扣。CPU仍然需要花费大量时间等待数据从内存中加载。内存带宽(单位时间内可以传输的数据量)和内存延迟(从请求数据到数据到达的时间)成为了这类应用的性能瓶颈。

1.1.4 并行计算的必然性

面对功耗墙、ILP墙和内存墙这“三座大山”,依靠传统的单核性能提升路径已经难以为继。计算机体系结构的发展方向必然转向更显式的并行计算。与其将一个核心做得越来越复杂、频率越来越高,不如集成更多的、相对简单一些的核心,让它们协同工作。

并行计算的类型主要有:

位级并行 (Bit-Level Parallelism):在单个指令中处理更多的数据位。例如,从8位处理器到16位、32位、64位处理器,使得一次可以处理更大范围的整数或更精确的浮点数。这一层次的并行性在现代处理器中已经基本饱和。

指令级并行 (Instruction-Level Parallelism, ILP):如前所述,CPU内部自动挖掘。

数据并行 (Data Parallelism):对大规模数据集中的不同部分同时执行相同的操作。这是GPU的核心优势所在。

任务并行 (Task Parallelism):将一个复杂的任务分解成多个可以独立或部分独立执行的子任务,分配给不同的处理器执行。多核CPU擅长处理这种类型的并行。

线程级并行 (Thread-Level Parallelism, TLP):通过多线程技术,在一个进程内创建多个执行流,这些线程可以并发(在单核上分时复用)或并行(在多核上同时)执行。

进程级并行 (Process-Level Parallelism):同时运行多个独立的程序(进程)。

多核CPU的出现就是为了更好地利用任务并行和线程级并行。然而,对于那些具有海量数据并行性的问题,CPU核心数量(通常在几个到几十个)与GPU核心数量(成百上千甚至上万)相比,仍然显得力不从心。

1.2 GPU的崛起:从图形渲染到通用计算的华丽转身

图形处理器(GPU)的发展历程与CPU有所不同,它最初的驱动力是日益增长的电子游戏和专业图形应用对实时三维图形渲染的需求。

1.2.1 图形渲染的并行本质

理解GPU为何适合并行计算,首先要理解图形渲染的基本流程和其内在的并行性。一个简化的三维图形渲染管线(Graphics Pipeline)通常包括以下阶段:

顶点处理 (Vertex Processing):

输入:三维模型的顶点坐标、颜色、纹理坐标、法向量等属性。

操作:对每个顶点进行模型变换(将物体从模型空间转换到世界空间)、视图变换(将物体从世界空间转换到观察者视角空间)、投影变换(将三维场景投影到二维屏幕)、光照计算(根据光源和材质计算顶点颜色)等。

并行性:每个顶点的处理通常是相互独立的,可以并行进行。一个复杂的场景可能有数百万个顶点。

图元组装 (Primitive Assembly):

将处理后的顶点组装成图元(如点、线段、三角形)。

进行裁剪(Clipping):去除视锥体(Viewing Frustum,即可见区域)之外的图元部分。

屏幕映射(Screen Mapping):将裁剪后的图元坐标转换到屏幕像素坐标。

光栅化 (Rasterization):

确定哪些像素点被每个图元(通常是三角形)所覆盖。

为被覆盖的像素生成片元(Fragment),片元包含了颜色、深度、纹理坐标等信息,这些信息是通过对三角形顶点属性进行插值得到的。

并行性:不同三角形的光栅化,以及同一三角形覆盖的不同像素的片元生成,都具有高度的并行性。

片元处理 (Fragment Processing / Pixel Shading):

输入:光栅化阶段生成的片元。

操作:对每个片元进行复杂的计算,例如:

纹理采样(Texture Mapping):根据片元的纹理坐标从纹理图中读取颜色值。

光照计算(Per-pixel Lighting):进行更精细的光照计算,考虑法线贴图、阴影等。

应用雾化、混合等效果。

并行性:每个片元的处理也是高度独立的。现代游戏屏幕分辨率很高(如1080p, 4K),每帧需要处理数百万甚至数千万个片元。

逐样本操作 (Per-Sample Operations):

进行深度测试(Z-buffering):比较片元的深度值与帧缓冲中对应像素已有的深度值,决定是否更新像素(处理遮挡关系)。

模板测试(Stencil Test):用于实现一些高级渲染效果。

颜色混合(Blending):将片元颜色与帧缓冲中已有的颜色进行混合(例如实现半透明效果)。

帧缓冲操作 (Framebuffer Operations):

最终的片元颜色被写入帧缓冲(Framebuffer),帧缓冲的内容最终显示在屏幕上。

从上述流程可以看出,图形渲染管线的核心阶段(顶点处理和片元处理)都涉及到对大量独立元素(顶点或片元)执行相似或相同的计算。这种计算模式天然适合大规模并行处理。

1.2.2 GPU架构的演进

为了满足这种并行需求,GPU的架构也朝着高度并行的方向发展:

早期GPU: 具有固定功能的硬件管线,每个阶段由专门的硬件单元处理。可编程性有限。

可编程着色器 (Programmable Shaders): 21世纪初,GPU开始引入可编程的顶点着色器(Vertex Shader)和像素着色器(Pixel Shader,或称片元着色器Fragment Shader)。开发者可以用专门的着色器语言(如GLSL for OpenGL, HLSL for DirectX, Cg for NVIDIA)编写小程序来控制顶点和片元的处理逻辑,这极大地增强了GPU的灵活性和图形效果的表现力。

此时的GPU架构通常包含一组并行的“着色器处理器(Shader Processors)”或“流处理器(Stream Processors, SP)”。

统一着色器架构 (Unified Shader Architecture): 后来,GPU厂商进一步发展了统一着色器架构。在这种架构下,不再区分专门的顶点处理单元和片元处理单元,而是使用一组通用的、可编程的处理单元,它们既可以执行顶点着色程序,也可以执行片元着色程序(以及后来的几何着色器、计算着色器等)。这提高了处理单元的利用率,因为可以根据当前负载动态分配处理资源。NVIDIA的GeForce 8系列(采用Tesla架构)是统一着色器架构的早期代表。

这些通用的、可编程的、数量众多的处理单元,正是GPU能够进行通用计算的硬件基础。它们的设计目标是:

高吞吐量 (High Throughput):GPU的核心设计哲学是最大化并行任务的吞吐量。它拥有非常多的计算核心(Stream Processors, SPs,或称CUDA Cores),这些核心可能不如CPU核心那么强大和复杂(例如,它们可能没有复杂的乱序执行逻辑或大型缓存),但它们的数量弥补了这一点。

高内存带宽 (High Memory Bandwidth):为了给众多的计算核心喂饱数据,现代GPU通常配备了专用的高速显存(如GDDR5, GDDR6, HBM),并通过宽位宽的内存总线与之连接,提供了远高于CPU主内存的带宽。

SIMD/SIMT执行模型: GPU的执行模型通常是单指令多数据(SIMD)或更准确地说是单指令多线程(SIMT)。一组线程(在NVIDIA CUDA中称为一个Warp,通常是32个线程)会同时执行相同的指令,但每个线程处理的数据不同。这种模型非常适合数据并行任务。

1.2.3 GPGPU的探索与早期实践

在CUDA出现之前,一些研究者和开发者已经开始尝试将GPU用于通用计算。他们通常需要将计算问题巧妙地“伪装”成图形渲染问题,利用顶点着色器或片元着色器来执行计算,并将输入数据编码成纹理,计算结果也输出为纹理,然后再从纹理中读回。这个过程非常复杂和繁琐,需要深入理解图形API和GPU的底层细节,限制了GPGPU的普及。

一些早期的GPGPU框架和语言(如BrookGPU, Sh)试图简化这个过程,但仍然有较高的学习曲线。

1.3 CUDA:NVIDIA开启的并行计算新纪元

NVIDIA敏锐地洞察到GPGPU的巨大潜力,并于2006年推出了CUDA(Compute Unified Device Architecture)。CUDA不仅仅是一个硬件架构的名称,更是一个完整的并行计算平台和编程模型。它的目标是让开发者能够更容易地利用NVIDIA GPU的强大并行计算能力来解决各种复杂的计算问题,而不仅仅是图形渲染。

1.3.1 CUDA的核心理念与组件

CUDA平台的核心组件和理念包括:

统一的计算设备架构:

NVIDIA的GPU(从G80架构开始,如GeForce 8800 GTX)被设计为可执行通用计算任务的并行处理器。

GPU包含多个流多处理器 (Streaming Multiprocessors, SMs)。每个SM内部又包含多个标量处理器 (Scalar Processors, SPs),也称为CUDA核心 (CUDA Cores)。例如,一个SM可能包含32、64、128或更多CUDA核心。

SM还包含共享内存、寄存器文件、特殊功能单元(SFUs,用于超越函数计算)、纹理单元等。

C/C++ (及后续语言) 作为编程语言:

CUDA允许开发者使用扩展的C/C++语言(通常称为CUDA C/C++)来编写在GPU上执行的并行代码(称为内核,Kernel)。这大大降低了GPGPU的编程门槛,因为C/C++是许多科学和工程领域开发者熟悉的语言。

后来,CUDA也增加了对Fortran的支持,并通过各种库和编译器扩展支持了Python等其他语言。

NVCC编译器:

NVIDIA提供了一个专门的编译器nvcc。nvcc负责将包含主机代码(在CPU上运行)和设备代码(在GPU上运行的Kernel)的源文件进行编译。

它会将主机代码交给标准的C/C++编译器(如GCC, MSVC, Clang)处理,将设备代码编译成GPU可执行的PTX(Parallel Thread Execution,一种中间汇编语言)或直接编译成特定GPU架构的二进制机器码(SASS)。

CUDA运行时API (Runtime API) 和驱动API (Driver API):

CUDA提供了两套API供开发者与GPU交互:

Runtime API: 更高层次、更易用的API,通常以cuda*前缀命名(例如cudaMalloc, cudaMemcpy, cudaLaunchKernel)。它隐式处理了许多上下文管理和设备初始化的细节。大部分应用开发者会使用Runtime API。

Driver API: 更低层次、更灵活的API,通常以cu*前缀命名(例如cuInit, cuDeviceGet, cuCtxCreate, cuModuleLoad, cuLaunchKernel)。它提供了对GPU更精细的控制,例如多设备管理、上下文管理、模块加载等。cuda-python库主要就是对Driver API的绑定。

Runtime API本身是在Driver API之上构建的一层封装。

线程组织 (Thread Hierarchy):

CUDA编程模型的核心是层次化的线程组织:

Kernel: 在GPU上执行的并行函数。

Grid: 一个Kernel在启动时会以一个Grid的形式执行。一个Grid由多个线程块 (Blocks) 组成。Grid可以是一维、二维或三维的。

Block: 一个线程块由多个线程 (Threads) 组成。一个Block内的线程可以相互协作,例如通过共享内存交换数据,通过同步原语(__syncthreads())进行同步。Block也可以是一维、二维或三维的。

Thread: 最基本的执行单元。每个线程执行相同的Kernel代码,但通过其唯一的线程ID(threadIdx)、块ID(blockIdx)、块维度(blockDim)和网格维度(gridDim)来区分自己,并处理不同的数据。

Warp: 在SM内部,线程是以Warp(通常是32个线程)为单位进行调度和执行的。一个Warp中的所有线程同时执行相同的指令(SIMT模型)。

内存模型 (Memory Hierarchy):

CUDA暴露了GPU上复杂的内存层次结构,允许开发者进行精细的优化:

寄存器 (Registers):每个线程私有的、速度最快的片上内存。

本地内存 (Local Memory):逻辑上是每个线程私有的,但物理上通常存储在设备全局内存(DRAM)中。当寄存器不足以存放线程的局部变量或发生数组溢出到本地内存时使用。访问速度较慢。

共享内存 (Shared Memory):每个线程块内的所有线程共享的、速度很快的片上内存。是线程块内线程间高效通信和数据共享的关键。其生命周期与线程块相同。

全局内存 (Global Memory):GPU上最大容量的内存(即显存,DRAM),所有线程块和所有线程都可以访问。主机(CPU)也可以通过PCIe总线读写全局内存。访问延迟较高,带宽是关键。

常量内存 (Constant Memory):只读的、由主机初始化、被所有线程块缓存的内存。适合存放所有线程都会读取的常量数据。

纹理内存 (Texture Memory):针对2D/3D空间局部性进行优化的只读缓存内存,支持特定的寻址模式和滤波操作。

理解并有效利用这个内存层次是CUDA程序性能优化的核心。

丰富的库支持:

NVIDIA提供了大量基于CUDA构建的高性能库,涵盖了各个领域:

cuBLAS: GPU加速的基本线性代数子程序库 (BLAS)。

cuSPARSE: GPU加速的稀疏矩阵运算库。

cuFFT: GPU加速的快速傅里叶变换库。

cuRAND: GPU加速的随机数生成库。

cuDNN: NVIDIA CUDA Deep Neural Network library,为深度学习框架提供高度优化的卷积、池化、激活等操作。

Thrust: 基于C++模板的并行算法库,提供了类似STL的接口,用于在GPU上进行数据并行操作(如排序、扫描、归约)。

NPP (NVIDIA Performance Primitives): 图像处理和信号处理的GPU加速函数库。

这些库经过NVIDIA工程师的深度优化,通常能提供比开发者自己编写内核更高的性能。

1.3.2 CUDA的优势与影响

CUDA的推出迅速改变了高性能计算的格局:

性能大幅提升: 对于适合并行化的应用,GPU(通过CUDA)可以提供相对于传统CPU数十倍甚至上百倍的性能提升。

应用领域拓展: 从最初的科学计算(如分子动力学、天体物理模拟、计算流体力学),迅速扩展到金融建模、图像视频处理、密码学、生物信息学、以及最重要的——机器学习和深度学习。

推动AI革命: 深度学习模型的训练需要海量的计算资源,尤其是矩阵运算。GPU的并行计算能力与深度学习的需求完美契合。可以说,没有CUDA和NVIDIA GPU的普及,当前的AI革命可能不会如此迅猛。

生态系统繁荣: CUDA吸引了大量的开发者、研究机构和商业公司投入,形成了庞大而活跃的生态系统。主流的深度学习框架(TensorFlow, PyTorch, Caffe, MXNet等)都深度依赖CUDA。

编程模型成为事实标准: 尽管有OpenCL等开放标准存在,但在NVIDIA GPU上,CUDA凭借其性能、成熟度和生态系统的优势,成为了事实上的主流并行编程模型。

1.4 Python:胶水语言与科学计算的宠儿

在我们讨论将GPU的计算能力引入Python之前,有必要强调一下Python语言本身在科学计算和数据驱动领域所扮演的关键角色。

1.4.1 Python的特性使其广受欢迎

语法简洁,易于学习: Python的语法设计力求清晰、简洁、易读,接近伪代码。这使得初学者可以快速上手,也使得有经验的开发者可以高效地表达复杂的逻辑。

# Python 列表推导式示例,简洁明了

squares = [x**2 for x in range(10) if x % 2 == 0] # 计算0-9中偶数的平方

print(squares) # 输出: [0, 4, 16, 36, 64]

动态类型,解释执行: Python是动态类型语言,变量类型在运行时确定,无需显式声明。它通常是解释执行的(尽管有JIT编译器如PyPy和Numba),这使得开发和调试周期更快。

“自带电池” (Batteries Included): Python拥有一个庞大且功能丰富的标准库,涵盖了网络、文件处理、操作系统交互、数据结构、文本处理等方方面面,开发者无需从零开始构建许多基础功能。

强大的“胶水”能力: Python非常容易与其他语言(如C, C++, Fortran)编写的代码进行集成。通过ctypes, cffi, SWIG, Cython, PyBind11等工具,可以将高性能的底层库封装成Python模块,让Python代码可以方便地调用。这是Python能够在性能敏感领域(如科学计算)取得成功的关键因素之一。

面向对象与函数式编程支持: Python支持多种编程范式,包括面向对象编程(OOP)和函数式编程(FP),开发者可以根据问题选择合适的风格。

跨平台性: Python代码通常可以不加修改或稍作修改就在多种操作系统(Windows, Linux, macOS)上运行。

1.4.2 Python在科学计算和数据科学领域的统治地位

正因为上述特性,Python在科学计算、数据分析、机器学习、人工智能等领域获得了巨大的成功,并逐渐成为这些领域的主流编程语言。其成功离不开一个强大的科学计算生态系统:

NumPy (Numerical Python):

提供了一个核心的多维数组对象 (ndarray),以及对这些数组进行高效操作的函数和方法。

底层通常使用C或Fortran实现,性能很高。

是Python中进行数值计算的基础。几乎所有其他科学计算库都依赖于NumPy。

import numpy as np # 导入numpy库

a = np.array([1, 2, 3, 4]) # 创建一个numpy数组

b = np.array([5, 6, 7, 8]) # 创建另一个numpy数组

c = a + b # 数组间的逐元素加法 (高效)

d = np.dot(a, b) # 计算点积

print(f"c = {

c}") # 输出: c = [ 6 8 10 12]

print(f"d = {

d}") # 输出: d = 70

SciPy (Scientific Python):

构建在NumPy之上,提供了大量用于科学和工程计算的模块,例如:

scipy.linalg: 线性代数例程(比numpy.linalg更完整)。

scipy.optimize: 优化算法(如函数最小化、曲线拟合)。

scipy.stats: 统计函数和概率分布。

scipy.integrate: 数值积分。

scipy.fft: 快速傅里叶变换。

scipy.signal: 信号处理工具。

scipy.sparse: 稀疏矩阵及其运算。

scipy.interpolate: 插值工具。

Pandas:

提供了高性能、易用的数据结构(如Series和DataFrame)和数据分析工具。

非常适合处理结构化(表格化)数据,进行数据清洗、转换、聚合、合并等操作。

在数据预处理和探索性数据分析中扮演核心角色。

Matplotlib:

一个广泛使用的Python 2D绘图库,可以生成出版质量级别的图表、直方图、散点图等。

Seaborn等库基于Matplotlib提供了更高级的统计可视化接口。

Scikit-learn:

一个简单高效的机器学习库,包含了大量的分类、回归、聚类、降维、模型选择和预处理工具。

API设计一致且易用。

Jupyter Notebook / JupyterLab:

一个基于Web的交互式计算环境,允许用户创建和共享包含实时代码、方程式、可视化和叙述文本的文档。

极大地促进了可重复性研究和数据科学的教学与协作。

深度学习框架:

TensorFlow (Google) 和 PyTorch (Facebook/Meta) 是目前最主流的两个深度学习框架。它们都选择Python作为主要的上层API语言,使得研究人员和开发者可以方便地定义、训练和部署复杂的神经网络模型。

Keras则提供了一个更高级、更易用的神经网络API,可以运行在TensorFlow等后端之上。

JAX是Google推出的一个新的用于高性能数值计算和机器学习研究的Python库,支持自动微分、JIT编译和在CPU/GPU/TPU上的执行。

Python凭借其易用性和强大的科学计算生态,使得许多原本需要专门领域知识和复杂编程的计算任务变得更加平易近人。然而,当面对海量数据和计算密集型任务时,纯Python(CPython解释器)的执行速度往往成为瓶颈。虽然NumPy等库的底层是用C/Fortran实现的,能够提供很好的性能,但对于那些无法轻易向量化(vectorize)或需要自定义复杂循环的计算,性能问题依然存在。这就是GPU加速的切入点。

1.5 CUDA与Python的结合:强强联手,释放GPU潜能

将NVIDIA CUDA的强大并行计算能力与Python的易用性和丰富的生态系统相结合,无疑是一个极具吸引力的方向。这使得Python开发者能够:

加速现有的Python计算任务: 对于那些在CPU上运行缓慢的数值计算、数据处理或模拟任务,如果其本质上是数据并行的,就有可能通过GPU加速获得显著的性能提升。

处理更大规模的问题: GPU通常拥有比CPU主内存带宽高得多的显存,并且其并行处理能力更适合处理TB级别甚至PB级别的数据集(当然,数据传输是瓶颈)。

探索新的算法和模型: 当计算不再是主要障碍时,研究人员可以更自由地尝试更复杂、计算量更大的算法和模型。

保持Python的开发效率: 理想情况下,开发者可以在不完全放弃Python的简洁性和生态优势的前提下,获得GPU的性能。

在“原生”CUDA Python支持(如cuda-python库)变得成熟之前,Python开发者主要通过以下几种方式利用GPU的CUDA能力:

1.5.1 PyCUDA 和 PyOpenCL

PyCUDA: 由Andreas Kloeckner开发,它提供了对NVIDIA CUDA C/C++ API(主要是Driver API)的Python封装。

允许开发者在Python中分配GPU内存,在CPU和GPU之间传输数据,加载和编译CUDA C/C++内核代码(通常以字符串形式嵌入Python代码中,或从外部文件加载),启动内核,以及管理CUDA流和事件。

开发者仍然需要用CUDA C/C++(或其变体,如通过Elementwise Kernel模板)来编写实际在GPU上执行的并行内核。

需要用户对CUDA编程模型和C/C++有相当的了解。

提供了SourceModule、CompileError、GPUArray等核心类。

# PyCUDA 伪代码示例 (仅为说明概念)

# import pycuda.autoinit # 自动初始化CUDA上下文

# import pycuda.driver as cuda # 导入CUDA驱动API的封装

# import numpy as np

# from pycuda.compiler import SourceModule # 用于从源码编译CUDA内核

# a_cpu = np.random.randn(400).astype(np.float32) # 在CPU上创建一个随机数数组

# a_gpu = cuda.mem_alloc(a_cpu.nbytes) # 在GPU上分配与a_cpu同样大小的内存

# cuda.memcpy_htod(a_gpu, a_cpu) # 将CPU上的数据a_cpu拷贝到GPU上的a_gpu

# kernel_code = """

# __global__ void double_elements(float *a) {

# int idx = threadIdx.x + blockIdx.x * blockDim.x;

# a[idx] *= 2.0f;

# }

# """ # 定义一个CUDA C内核代码字符串,该内核将数组中的每个元素乘以2

# mod = SourceModule(kernel_code) # 从源码编译CUDA内核

# double_func = mod.get_function("double_elements") # 获取编译后的内核函数

# block_size = (256, 1, 1) # 定义线程块大小 (256个线程)

# grid_size = ((a_cpu.size + block_size[0] - 1) // block_size[0], 1) # 定义线程网格大小

# double_func(a_gpu, block=block_size, grid=grid_size) # 在GPU上启动内核函数

# result_gpu = np.empty_like(a_cpu) # 在CPU上创建一个与a_cpu形状相同的空数组,用于存放结果

# cuda.memcpy_dtoh(result_gpu, a_gpu) # 将GPU上的结果a_gpu拷贝回CPU上的result_gpu

# print(result_gpu) # 打印结果

PyOpenCL: 同样由Andreas Kloeckner开发,它提供了对OpenCL (Open Computing Language) API的Python封装。OpenCL是一个开放的、跨平台的并行编程标准,可以在包括NVIDIA GPU、AMD GPU、Intel CPU/GPU等多种异构硬件上运行。

与PyCUDA类似,开发者需要用OpenCL C(一种基于C99的语言)编写内核。

如果需要跨多种硬件平台的GPU代码可移植性,OpenCL是一个选项,但通常在NVIDIA GPU上,CUDA的性能和生态系统更占优势。

PyCUDA和PyOpenCL为Python打开了通向底层GPU编程的大门,但它们仍然要求开发者直接处理GPU编程的复杂性(如内存管理、内核编写、同步等)。

1.5.2 Numba

Numba是一个开源的、基于LLVM的Python JIT(Just-In-Time)编译器,由Anaconda公司(原Continuum Analytics)支持开发。Numba可以将Python函数(尤其是那些使用NumPy数组和进行循环计算的函数)编译成高效的机器码,其性能可以接近甚至达到C或Fortran的水平。

Numba的一个重要特性是它对NVIDIA GPU的CUDA编程提供了直接支持:

@cuda.jit 装饰器: 开发者可以用这个装饰器来标记一个Python函数,Numba会尝试将其编译成CUDA内核在GPU上执行。

内核函数内部通常使用Numba提供的CUDA API子集,例如cuda.threadIdx, cuda.blockIdx, cuda.shared.array, cuda.syncthreads()等,这些API的风格与CUDA C/C++非常相似,但都是在Python语法框架内。

Numba会处理内核的编译(通常在首次调用时)和加载。

支持的数据类型通常是标量和NumPy数组(或Numba的CUDA设备数组)。

自动内存传输 (可选): 当将NumPy数组作为参数传递给@cuda.jit内核时,Numba可以自动处理CPU和GPU之间的数据传输,简化了开发。当然,也可以进行显式的内存分配和拷贝以获得更精细的控制。

GPU设备函数: Numba也支持通过@cuda.jit(device=True)定义只能从GPU内核中调用的设备函数,方便代码复用。

支持部分Python特性: Numba CUDA支持Python的循环、条件判断、基本算术运算、以及一些数学函数。但它支持的Python语言特性是有限的,复杂的Python对象或标准库功能可能无法在内核中使用。

import numpy as np # 导入numpy库

from numba import cuda # 从numba库导入cuda模块

@cuda.jit # 使用numba的cuda.jit装饰器来定义一个将在GPU上执行的内核函数

def add_kernel_numba(x, y, out): # 内核函数,接收三个数组作为参数

"""

一个简单的Numba CUDA内核,计算 out = x + y。

"""

idx = cuda.grid(1) # 获取当前线程在整个网格中的一维索引

# cuda.grid(1) 等价于 cuda.threadIdx.x + cuda.blockIdx.x * cuda.blockDim.x

if idx < x.shape[0]: # 检查索引是否越界 (防止处理数组末尾的多余线程)

out[idx] = x[idx] + y[idx] # 执行逐元素加法

# --- 主机代码 ---

N = 1024 * 1024 # 定义数组大小 (约一百万)

x_cpu = np.arange(N, dtype=np.float32) # 在CPU上创建数组x

y_cpu = np.ones(N, dtype=np.float32) * 2 # 在CPU上创建数组y

# 1. 将数据从CPU拷贝到GPU (Numba可以隐式处理,但显式更清晰)

# x_gpu = cuda.to_device(x_cpu) # 将x_cpu拷贝到GPU设备内存

# y_gpu = cuda.to_device(y_cpu) # 将y_cpu拷贝到GPU设备内存

# out_gpu = cuda.device_array_like(x_gpu) # 在GPU上创建一个与x_gpu形状和类型相同的空数组

# 2. 配置内核启动参数

threads_per_block = 256 # 定义每个线程块包含的线程数

blocks_per_grid = (N + (threads_per_block - 1)) // threads_per_block # 计算所需的线程块数量,确保覆盖所有元素

# 3. 启动内核

# Numba 会自动处理 x_cpu, y_cpu 到GPU的拷贝,以及 out_gpu 的创建和结果拷贝回 out_cpu (如果直接传NumPy数组)

# 或者我们可以传递已在GPU上的数组

out_cpu_numba = np.empty_like(x_cpu) # 在CPU上创建用于接收结果的数组

add_kernel_numba[blocks_per_grid, threads_per_block](x_cpu, y_cpu, out_cpu_numba) # 启动内核

# (如果使用显式GPU数组)

# add_kernel_numba[blocks_per_grid, threads_per_block](x_gpu, y_gpu, out_gpu)

# out_cpu_numba = out_gpu.copy_to_host() # 将GPU上的结果拷贝回CPU

print(f"Numba CUDA result (first 5): {

out_cpu_numba[:5]}") # 打印结果的前5个元素

# 预期: [2. 3. 4. 5. 6.]

# 检查结果

# if np.allclose(out_cpu_numba, x_cpu + y_cpu):

# print("Numba CUDA computation successful!")

# else:

# print("Numba CUDA computation failed!")

Numba极大地简化了用Python编写CUDA内核的过程,使得开发者可以更专注于算法逻辑而不是底层的CUDA C API细节。它是目前Python生态中最流行的编写自定义CUDA内核的方式之一。

1.5.3 CuPy

CuPy是一个开源的GPU数组库,它实现了与NumPy高度兼容的API。如果你熟悉NumPy,那么使用CuPy会感觉非常自然。CuPy的目标是让用户能够用类似NumPy的语法在NVIDIA GPU上执行计算。

NumPy兼容接口: CuPy中的许多函数和方法与NumPy中的同名,参数也类似。例如,cp.array(), cp.add(), cp.linalg.solve()等。

GPU数组 (cupy.ndarray): CuPy的核心数据结构是cupy.ndarray,它在GPU显存中存储数据。

自动内核生成/调用: 当你对CuPy数组执行操作时(例如z = cp.sin(x) + cp.cos(y)),CuPy会在后台自动选择或生成并启动相应的CUDA内核来执行这些计算。用户通常不需要直接编写CUDA内核代码。

用户自定义内核: CuPy也允许用户编写自定义的CUDA内核(通常是CUDA C/C++代码字符串,类似于PyCUDA的RawKernel,或者使用ElementwiseKernel等更高级的抽象),并从Python中调用它们作用于CuPy数组。

与NumPy的互操作: 可以方便地在CuPy数组和NumPy数组之间拷贝数据(通过cp.asarray()从NumPy到CuPy,通过cupy.ndarray.get()或cp.asnumpy()从CuPy到NumPy)。

流和事件: CuPy也支持CUDA流和事件,允许进行异步操作和更精细的执行控制。

import numpy as np # 导入numpy库

import cupy as cp # 导入cupy库

import time # 导入time模块

N = 1024 * 1024 * 10 # 定义数组大小 (一千万)

# 使用NumPy在CPU上执行

x_cpu_np = np.random.rand(N).astype(np.float32) # 在CPU上创建随机数组x

y_cpu_np = np.random.rand(N).astype(np.float32) # 在CPU上创建随机数组y

start_time_cpu = time.time() # 记录CPU开始时间

z_cpu_np = np.sin(x_cpu_np**2) + np.cos(y_cpu_np**2) # 在CPU上执行计算

end_time_cpu = time.time() # 记录CPU结束时间

print(f"NumPy (CPU) time: {

end_time_cpu - start_time_cpu:.4f} seconds") # 打印CPU执行时间

# 使用CuPy在GPU上执行

# 1. 将数据从CPU拷贝到GPU

x_gpu_cp = cp.asarray(x_cpu_np) # 将x_cpu_np拷贝到GPU (创建CuPy数组)

y_gpu_cp = cp.asarray(y_cpu_np) # 将y_cpu_np拷贝到GPU (创建CuPy数组)

cp.cuda.Device(0).synchronize() # 等待当前设备(GPU 0)上的所有操作完成,确保拷贝完成 (用于计时准确性)

start_time_gpu = time.time() # 记录GPU开始时间

z_gpu_cp = cp.sin(x_gpu_cp**2) + cp.cos(y_gpu_cp**2) # 在GPU上执行计算 (语法与NumPy几乎一样)

cp.cuda.Device(0).synchronize() # 等待GPU计算完成 (对于计时是必要的)

end_time_gpu = time.time() # 记录GPU结束时间

print(f"CuPy (GPU) time: {

end_time_gpu - start_time_gpu:.4f} seconds") # 打印GPU执行时间

# 2. (可选) 将结果从GPU拷贝回CPU

# z_cpu_from_gpu = cp.asnumpy(z_gpu_cp) # 或者 z_cpu_from_gpu = z_gpu_cp.get()

# 检查结果是否一致 (需要将GPU结果拷回CPU)

# if np.allclose(z_cpu_np, z_cpu_from_gpu, atol=1e-6):

# print("CuPy computation matches NumPy!")

# else:

# print("CuPy computation MISMATCH!")

# 清理GPU内存 (CuPy数组超出作用域时会自动释放,但也可以显式操作)

# del x_gpu_cp, y_gpu_cp, z_gpu_cp

# cp.get_default_memory_pool().free_all_blocks() # 清理内存池

CuPy对于那些已经熟悉NumPy并且其计算任务可以很好地映射到NumPy API的开发者来说,是一个非常快速的GPU加速入门方式。它隐藏了大部分CUDA编程的复杂性。

1.5.4 深度学习框架 (TensorFlow, PyTorch)

如前所述,TensorFlow和PyTorch是驱动当前AI革命的核心框架。它们都将Python作为主要的上层API,并且能够无缝地在CPU和NVIDIA GPU上执行计算。

张量 (Tensors): 它们的核心数据结构是张量,可以看作是多维数组,类似于NumPy的ndarray或CuPy的cupy.ndarray。

自动微分 (Automatic Differentiation): 这是训练神经网络的关键,框架能够自动计算损失函数相对于模型参数的梯度。

计算图 (Computation Graphs): TensorFlow(尤其是在1.x版本)使用静态或动态计算图来表示计算流程。PyTorch主要使用动态计算图,更具灵活性。

GPU后端: 当检测到可用的NVIDIA GPU并正确配置后,这些框架会将张量数据存储在GPU显存中,并调用高度优化的CUDA内核(很多来自cuDNN, cuBLAS等库)来执行神经网络的各种操作(如卷积、矩阵乘法、激活函数等)。

用户透明性: 大部分情况下,用户只需要指定希望在哪种设备上执行计算(例如,tensor.to('cuda')),框架会自动处理底层的CUDA调用和数据传输。用户几乎不需要直接编写CUDA代码。

# PyTorch 伪代码示例

# import torch # 导入torch库

# device = torch.device("cuda" if torch.cuda.is_available() else "cpu") # 检查CUDA是否可用,并设置设备

# print(f"Using device: {device}") # 打印正在使用的设备

# x = torch.randn(1000, 1000, device=device) # 在选定设备上创建一个1000x1000的随机张量

# y = torch.randn(1000, 1000, device=device) # 在选定设备上创建另一个1000x1000的随机张量

# # 执行张量运算

# start_time_torch = time.time() # 记录开始时间

# for _ in range(100): # 执行100次矩阵乘法

# z = torch.matmul(x, y) # 执行矩阵乘法

# torch.cuda.synchronize() # (如果设备是cuda) 等待所有CUDA操作完成,确保计时准确

# end_time_torch = time.time() # 记录结束时间

# print(f"PyTorch ({device}) 100 matmuls time: {end_time_torch - start_time_torch:.4f} seconds") # 打印执行时间

# print(z.shape) # 打印结果张量的形状

深度学习框架为AI领域的GPU加速提供了极大的便利,但它们通常是针对神经网络这种特定计算模式进行优化的。对于更通用的科学计算或自定义并行算法,可能还需要PyCUDA, Numba或CuPy这类工具。

第二章:深入学习CUDA的硬件架构和核心编程模型,为后续的Python实践打下坚实的理论基础

理解硬件架构,如同庖丁解牛,能够让我们洞悉GPU为何能实现如此惊人的并行处理能力。我们将深入探索GPU内部的组织结构,从宏观的整体设计到微观的计算单元,剖析数据如何在不同的内存层级间流转,以及任务是如何被调度和执行的。这部分知识将帮助我们理解编写高效CUDA程序时,为何某些策略可行而另一些则不然,例如,为何要已关注数据局部性、为何要避免线程束分化等。

掌握CUDA编程模型,则如同学习一门新的语言范式。它定义了开发者如何与GPU进行交互,如何组织并行任务,如何管理内存,以及如何协调成千上万个线程的同步执行。我们将详细学习线程的层次结构(Grid、Block、Thread)、内存的分类与使用(全局内存、共享内存、常量内存等)、核函数的定义与启动,以及SIMT(单指令多线程)这一核心执行模式。这些概念是编写任何CUDA程序,无论是使用C++还是Python封装库,都必须牢固掌握的基础。

2.1 CUDA硬件架构概览:从宏观到微观

要充分发挥GPU的计算潜力,首先需要理解其内部的“构造”。与主要为串行任务和复杂控制流而优化的CPU不同,GPU的设计核心在于大规模并行处理和高吞吐量计算。这种设计哲学的差异直接体现在其硬件架构上。本节将带领读者从宏观视角审视现代GPU的整体架构,逐步深入到构成其计算能力的核心单元——流式多处理器(Streaming Multiprocessor, SM),并详细解析GPU的内存层次结构以及其独特的硬件线程管理机制。我们还将回顾NVIDIA GPU架构的演进历程,理解不同代际架构在设计上的侧重与革新,以及这些变化对CUDA编程实践带来的影响。

2.1.1 GPU的演进与现代GPU的通用计算架构特性

图形处理器(GPU)的诞生最初是为了满足日益增长的计算机图形渲染需求。早期的GPU主要是固定功能的硬件流水线,用于加速特定的图形操作,如顶点变换、光栅化和纹理映射。它们的编程接口(如OpenGL和Direct3D的早期版本)也主要面向图形渲染任务,其通用计算能力非常有限。开发者如果想利用GPU进行非图形计算,往往需要将问题“伪装”成图形渲染问题,例如将数据存储在纹理中,通过像素着色器进行计算,这无疑增加了编程的复杂性和局限性。

然而,随着时间的推移,研究人员和工程师们逐渐意识到,GPU内部蕴含的巨大并行计算潜力远不止于图形渲染。GPU拥有数百甚至数千个小型计算核心,能够同时执行大量的简单算术和逻辑运算,这使其在处理数据并行型任务时具有天然的优势。这种任务的特点是,可以将一个大的计算问题分解为许多独立的、可以同时处理的子问题。

从固定功能到可编程着色器时代:

GPU演进的一个关键转折点是可编程着色器(Programmable Shaders)的引入。最初的着色器主要用于控制渲染管线的特定阶段,如顶点处理(Vertex Shaders)和片元/像素处理(Fragment/Pixel Shaders)。开发者可以通过编写简短的类C语言(如HLSL, GLSL, Cg)程序来控制这些阶段的行为,实现更复杂和定制化的视觉效果。这标志着GPU从一个“黑盒式”的固定功能硬件,开始向一个更具灵活性和可编程性的计算设备转变。

尽管可编程着色器为GPU带来了更高的灵活性,但其设计初衷仍然是服务于图形渲染流程。着色器语言在数据类型、控制流、内存访问等方面存在诸多限制,直接将其用于通用计算(General-Purpose computing on GPUs, GPGPU)仍然不够理想。例如,早期的着色器可能缺乏对整数运算的良好支持,或者难以实现复杂的内存访问模式和线程间通信。

统一着色器架构的出现:

为了更好地支持通用计算,GPU架构经历了又一次重要的变革——统一着色器架构(Unified Shader Architecture)。在早期的非统一架构中,GPU内部针对顶点处理、几何处理、像素处理等不同任务设有专门的、独立的硬件单元。这种设计的缺点在于,当某一类型的任务负载较重,而其他类型的任务负载较轻时,专门负责轻负载任务的硬件单元就会闲置,导致资源利用率不高。

统一着色器架构则打破了这种专用硬件单元的划分。它引入了大量相同的、通用的可编程处理单元。这些单元不再局限于处理特定类型的着色任务,而是可以根据实际需求动态地分配给顶点、几何、像素着色或通用计算任务。这意味着,无论应用程序的瓶颈在哪个阶段,GPU都可以将尽可能多的计算资源投入到该阶段,从而显著提高了硬件的利用率和整体性能。NVIDIA的GeForce 8系列(采用Tesla架构)是首批采用统一着色器架构的GPU之一,这一架构的转变也为CUDA的诞生奠定了坚实的硬件基础。

现代GPU的通用计算架构特性:

在统一着色器架构的基础上,现代GPU为了更好地适应通用计算的需求,发展出了一系列关键的架构特性:

大规模并行核心 (Many-Core Architecture):

现代GPU通常集成数千个相对简单的算术逻辑单元(ALU),也称为CUDA核心(NVIDIA术语)或流处理器(AMD术语)。这些核心被组织成多个流式多处理器(SM)或计算单元(CU)。与CPU的少数几个强大的核心(擅长复杂控制流和低延迟串行任务)不同,GPU的众核设计使其能够同时执行海量的线程,实现极高的数据吞吐量。这种设计非常适合那些可以被分解为大量独立或松耦合计算子任务的问题,如矩阵运算、图像处理、物理模拟、深度学习等。

SIMT (Single Instruction, Multiple Threads) 执行模型:

GPU采用SIMT执行模型来管理和调度其众多的线程。在SIMT模型中,一组线程(在NVIDIA CUDA中称为一个线程束,Warp)同时执行相同的指令,但每个线程操作在不同的数据上。这种方式简化了指令获取和解码的硬件开销,同时保持了高度的并行性。我们将在后续章节详细讨论SIMT及其对编程的影响,例如分支分化(branch divergence)问题。

层次化的内存结构 (Hierarchical Memory System):

为了满足大规模并行计算对数据带宽和低延迟访问的需求,GPU设计了复杂的层次化内存系统。这通常包括:

片上寄存器 (On-chip Registers):每个核心私有,速度最快,但容量有限。

片上共享内存/L1缓存 (On-chip Shared Memory / L1 Cache):由一个SM内的所有核心共享,延迟较低,带宽较高,用户可编程控制(共享内存)或硬件管理(L1缓存)。共享内存对于线程块内的线程间高效协作至关重要。

L2缓存 (L2 Cache):由所有SM共享,容量更大,用于缓存对全局内存的访问,降低访存延迟。

全局内存 (Global Memory / Device Memory):通常是板载的大容量GDDR SDRAM,带宽很高但延迟也相对较高。所有SM都可以访问全局内存,是GPU上主要的数据存储区域。

常量内存 (Constant Memory) 和 纹理内存 (Texture Memory):具有特殊缓存机制的只读内存区域,用于优化特定类型的访存模式。

理解并有效利用这个内存层次结构是编写高性能CUDA程序的关键。

硬件线程调度器 (Hardware Thread Scheduler):

GPU拥有专门的硬件调度器,负责在SM内部创建、管理和调度成千上万个线程。这种硬件级线程管理使得线程切换的开销极低,几乎可以忽略不计。当一个线程束(Warp)因为等待内存访问(例如从全局内存读取数据)而阻塞时,SM可以迅速切换到另一个准备就绪的线程束继续执行计算,从而有效地隐藏内存延迟,保持计算单元的繁忙。这是GPU实现高吞吐量的重要机制之一。

专用硬件单元的集成 (Integration of Specialized Hardware Units):

随着应用需求的发展,现代GPU除了通用的CUDA核心外,还集成了越来越多的专用硬件单元以加速特定类型的计算。例如:

张量核心 (Tensor Cores):从Volta架构开始引入,专门用于加速深度学习中常见的混合精度矩阵乘法累加运算(MMA),显著提升了深度学习训练和推理的性能。

RT核心 (Ray Tracing Cores):从Turing架构开始引入,用于加速光线追踪计算中的光线与三角形求交测试(ray-triangle intersection)和包围盒层次结构遍历(Bounding Volume Hierarchy, BVH traversal),为实时光线追踪在游戏和专业渲染中的应用提供了硬件支持。

双精度浮点单元 (FP64 Cores):虽然消费级GPU可能对双精度性能有所削减以控制成本和功耗,但专业级和数据中心级GPU通常配备了更多的FP64单元,以满足科学计算、工程模拟等领域对高精度计算的需求。

高速互连技术 (High-Speed Interconnects):

PCI Express (PCIe):用于GPU与CPU主系统之间的数据通信。PCIe的带宽和延迟对整体应用性能有重要影响,尤其是在需要频繁进行主机-设备数据传输的应用中。PCIe标准的不断升级(如PCIe 3.0, 4.0, 5.0, 6.0)持续提升了带宽。

NVLink / NVSwitch (NVIDIA):NVIDIA开发的高速GPU间互连技术,提供远高于PCIe的带宽和更低的延迟,使得多个GPU能够更高效地协同工作,支持更大规模的模型训练和高性能计算任务。

异步计算与流 (Asynchronous Compute and Streams):

现代GPU支持异步操作,允许计算任务、内存拷贝任务等在不同的“流”(Streams)中并发执行,甚至可以与CPU的计算重叠。通过精心设计的任务流,可以进一步提高硬件资源的利用率和应用程序的整体性能。

GPU架构的这些演进和特性,使其从一个专门的图形加速器转变为一个强大的、通用的并行计算平台。CUDA编程模型正是建立在这样的硬件基础之上,为开发者提供了一套抽象,使其能够有效地驾驭GPU的并行计算能力。理解这些硬件特性,将有助于我们更好地理解CUDA编程模型为何如此设计,以及如何在实践中编写出能够充分发挥硬件潜能的Python CUDA程序。

例如,当我们讨论CUDA中的“线程块”(Thread Block)概念时,就会意识到它与SM的资源(如共享内存、寄存器数量)密切相关。当我们考虑内存访问优化时,就需要充分利用GPU的内存层次结构,将频繁访问的数据尽可能地放在靠近计算核心的低延迟内存中(如共享内存或寄存器)。当我们设计并行算法时,就需要考虑SIMT执行模型,尽量避免线程束内的分支分化,以确保所有线程都能高效执行。

接下来的小节将更具体地深入到SM的内部构造、GPU的内存体系以及线程管理机制中,为我们后续理解CUDA编程模型的核心概念打下更坚实的基础。

2.1.2 Streaming Multiprocessor (SM):GPU的计算核心

流式多处理器(Streaming Multiprocessor,简称SM)是NVIDIA GPU架构中的核心处理单元,是GPU执行并行计算任务的基本构建模块。可以将其理解为GPU内部的一个“迷你处理器”,但它本身又包含了多个更小的计算单元(CUDA核心)以及执行并行任务所需的各种资源。一个GPU通常由多个SM组成,SM的数量和每个SM的内部配置(如CUDA核心数量、寄存器文件大小、共享内存容量等)是区分不同型号和不同代次GPU性能的关键指标之一。

SM的宏观角色与设计理念:

SM的设计目标是在尽可能小的面积和功耗下,实现最大化的并行计算吞吐量。它通过以下方式实现这一目标:

执行大量线程:每个SM能够同时管理和执行数百甚至数千个CUDA线程。这些线程被组织成线程束(Warp),SM以Warp为单位进行调度和执行。

共享资源:SM内部的CUDA核心可以共享一些关键资源,如指令缓存、共享内存、L1缓存以及特殊功能单元。这种资源共享有助于提高利用率并减少冗余。

隐藏延迟:通过快速的上下文切换能力,当一个Warp因为等待数据(例如从全局内存读取)而暂停时,SM可以迅速切换到另一个已就绪的Warp继续执行计算,从而有效地隐藏内存访问延迟,保持计算核心的繁忙。

SM的内部构成:

一个SM的内部结构相当复杂,并且随着GPU架构的代代更新而不断演进。然而,其核心组成部分通常包括:

CUDA核心 (CUDA Cores / Scalar Processors, SPs):

这是SM内部最基本的计算单元,负责执行实际的算术和逻辑运算。每个CUDA核心通常能够执行单精度浮点(FP32)运算,部分架构也支持整数(INT32)运算。在更高级的GPU中,一些CUDA核心可能还具备双精度浮点(FP64)计算能力,但其数量通常远少于FP32核心,或者通过多个FP32核心组合来实现FP64运算。

CUDA核心的设计强调简单高效,以数量取胜。它们不像CPU核心那样拥有复杂的乱序执行、分支预测等逻辑,而是专注于大规模并行执行简单的指令。

特殊功能单元 (Special Function Units, SFUs):

SFU用于执行一些超越标准算术逻辑运算的复杂数学函数,例如正弦(sin)、余弦(cos)、指数(exp)、对数(log)、平方根倒数(1/sqrt(x))等。这些函数在图形渲染和科学计算中非常常用。将这些运算硬化到专门的SFU中,可以比通过一系列基本算术指令模拟实现要快得多,且功耗更低。每个SM通常包含若干个SFU。

张量核心 (Tensor Cores) (自Volta架构起):

张量核心是NVIDIA为加速深度学习工作负载而引入的专用处理单元。它们专门优化了混合精度矩阵乘积累加(Matrix Multiply-Accumulate, MMA)运算,即 (D = A imes B + C),其中A和B通常是FP16(半精度浮点)或INT8/INT4(8位/4位整数)矩阵,而累加结果C和D可以是FP16或FP32。

深度学习模型的训练和推理过程大量依赖此类矩阵运算。通过使用张量核心,可以在显著降低精度的同时(通常对模型准确率影响不大,甚至可以通过混合精度训练技术提升训练速度和稳定性),大幅提升运算速度并降低功耗。每个SM会集成一定数量的张量核心,其数量和能力也是衡量GPU深度学习性能的重要指标。例如,Hopper架构的第四代张量核心引入了对FP8数据类型的支持,进一步提升了效率。

RT核心 (Ray Tracing Cores) (自Turing架构起):

RT核心是为加速光线追踪计算而设计的专用硬件。光线追踪是一种模拟光线在场景中传播、反射和折射的渲染技术,能够产生高度逼真的图像,但计算量极大。RT核心主要加速两个关键操作:

光线-三角形求交 (Ray-Triangle Intersection Tests):判断一条光线是否与场景中的某个三角形相交。

包围盒层次加速结构遍历 (Bounding Volume Hierarchy Traversal):BVH是一种用于快速剔除大量不相关几何体的数据结构,RT核心可以高效地遍历BVH以快速找到可能与光线相交的物体。

通过RT核心,GPU能够以更高的帧率实现实时光线追踪效果,这对于游戏、影视特效和专业可视化领域意义重大。

指令缓存 (Instruction Cache / L0 Cache):

用于缓存最近执行的指令,减少从更高级别缓存或内存中获取指令的延迟。

寄存器文件 (Register File):

每个SM都拥有一个大容量的寄存器文件。寄存器是GPU上速度最快的存储单元,用于存放线程的私有数据、中间计算结果等。CUDA线程对寄存器的访问延迟极低(通常一个时钟周期)。寄存器文件的总容量是固定的,由SM内的所有活动线程共享。因此,每个线程可使用的寄存器数量是有限的,如果一个内核函数(Kernel)请求过多的寄存器,可能会导致“寄存器溢出”(Register Spilling),即部分本应存储在寄存器中的变量被迫存储到速度较慢的本地内存(Local Memory,实际上是全局内存的一部分)中,从而严重影响性能。编译器会尝试优化寄存器的使用,但程序员也需要已关注这一点。

共享内存 (Shared Memory / L1 Cache):

共享内存是SM内部的一块可编程的高速片上内存。它由同一个线程块(Thread Block)内的所有线程共享,并且具有远低于全局内存的访问延迟和更高的带宽。共享内存对于实现线程块内线程之间的高效数据交换和协作至关重要。程序员可以显式地在CUDA C/C++(或通过Python库的接口)中声明和使用共享内存。

在某些GPU架构中,一部分片上内存可以配置为L1缓存,另一部分配置为共享内存,或者两者共享同一物理存储但逻辑上分离。L1缓存由硬件自动管理,用于缓存对本地内存和全局内存的访问,对程序员透明。共享内存则需要程序员显式管理。合理利用共享内存是CUDA优化的一个核心技巧。

Warp调度器 (Warp Schedulers) / 派遣单元 (Dispatch Units):

每个SM包含一个或多个Warp调度器,负责选择当前已就绪的Warp(线程束)并将其指令发射到CUDA核心、SFU、张量核心或其他执行单元上。如前所述,当一个Warp遇到长延迟操作(如等待全局内存数据)时,调度器可以快速切换到另一个Warp,以保持计算单元的利用率。这种零开销或极低开销的上下文切换是GPU高效隐藏延迟的关键。调度器会跟踪每个Warp的状态(如就绪、等待、阻塞等)。

加载/存储单元 (Load/Store Units, LD/ST):

负责处理对各级内存(如全局内存、共享内存、常量内存、纹理内存)的读写请求。这些单元与内存控制器交互,执行数据的加载和存储操作。其效率直接影响GPU的内存带宽利用率。

SM内部的并行性层级:

一个SM内部本身就体现了多层次的并行性:

CUDA核心并行:SM内有多个CUDA核心,它们可以并行执行来自不同Warp或同一Warp内不同线程的算术指令。

Warp级并行 (Instruction Level Parallelism within a Warp – somewhat, but more about SIMT):一个Warp内的所有线程(通常是32个)同时执行相同的指令。

Warp间并行 (Warp-Level Parallelism / Thread-Level Parallelism):SM可以同时驻留(resident)多个Warp,并通过Warp调度器在它们之间快速切换,实现多个Warp的指令流在时间上的交错执行,从而隐藏延迟。

特殊单元并行:CUDA核心、SFU、张量核心、RT核心等可以根据指令类型并行工作。

不同GPU架构中SM的演进:

NVIDIA的GPU架构(如Fermi, Kepler, Maxwell, Pascal, Volta, Turing, Ampere, Hopper, Blackwell等)在每一代都会对SM的设计进行改进和增强。这些改进可能包括:

增加CUDA核心数量:直接提升SM的理论峰值计算能力。

改进CUDA核心设计:例如提升时钟频率、改进指令流水线、增强双精度性能等。

增大寄存器文件和共享内存容量:允许每个SM驻留更多的线程和线程块,或者允许每个线程使用更多的本地资源,从而提高并行度和灵活性。

引入新的专用硬件:如张量核心、RT核心。

改进Warp调度机制:例如增加每个SM的Warp调度器数量,或者提升调度算法的效率。

提升内存子系统性能:例如增加L1缓存带宽、降低共享内存访问延迟。

功耗优化:在提升性能的同时,努力控制甚至降低SM的功耗。

例如,从Fermi架构到Kepler架构,一个显著的变化是每个SM的CUDA核心数量大幅增加,但核心频率有所调整。Volta架构引入了张量核心,并重新设计了SM的调度方式,使其能够更好地支持混合精度计算和深度学习任务。Ampere架构进一步增加了每个SM的FP32核心数量(通过一种“双倍FP32”路径的设计,使得某些SM配置下,一个时钟周期内可以执行的FP32操作数翻倍),并增强了张量核心和RT核心的性能。Hopper架构则带来了第四代张量核心、新的SM设计(称为SM Next),以及对FP8数据类型和Transformer引擎的支持,进一步针对AI和HPC负载进行了优化。

理解SM的这些内部组件及其协同工作方式,对于CUDA程序员至关重要。例如,当你设计一个Kernel时,你需要考虑:

线程块大小(Block Size):一个线程块会被调度到单个SM上执行。块的大小(线程数量)会影响SM资源的分配,如共享内存和寄存器。如果块太大,可能因为资源不足而无法启动;如果太小,可能无法充分利用SM的并行能力。

共享内存的使用:如果你的算法需要在线程块内的线程间频繁共享数据,那么将这些数据显式地加载到共享内存中,可以大大提高性能。你需要规划共享内存的分配和访问模式。

寄存器使用量:编译器会报告每个线程使用的寄存器数量。如果过高,你需要考虑优化代码,减少临时变量,或者使用编译器选项来限制寄存器使用,以避免溢出。

指令类型:如果你的计算大量依赖于特定的数学函数,了解SFU的性能是有益的。如果你的应用是深度学习,那么如何有效地利用张量核心将是关键。

SM是GPU计算能力的引擎。通过深入理解其内部结构和运作机制,我们才能更好地驾驭这台强大的并行计算机器,编写出高效的CUDA程序。在后续讨论CUDA编程模型时,我们会不断回顾SM的这些特性,看它们是如何影响并行程序的组织和优化的。

代码示例:概念性理解SM资源限制

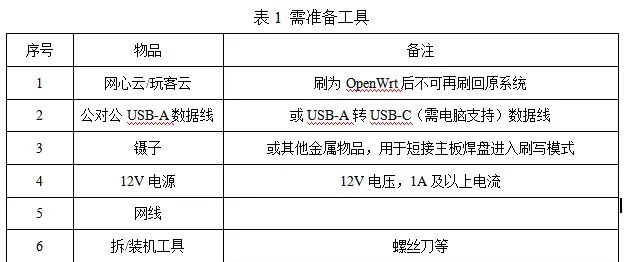

虽然我们还未深入到CUDA C++或Python CUDA编程,但可以通过一个概念性的伪代码来理解SM资源如何限制线程块的调度。

// 伪代码 - 概念演示SM资源限制

// 假设一个SM的资源如下:

MAX_THREADS_PER_SM = 2048; // SM最大并发线程数

MAX_BLOCKS_PER_SM = 32; // SM最大并发线程块数 (取决于资源)

SHARED_MEMORY_PER_SM = 96 * 1024; // SM可用共享内存总量 (96KB)

REGISTERS_PER_SM = 64 * 1024; // SM可用寄存器总量 (65536个32位寄存器)

// 假设我们定义了一个Kernel,其每个线程块的资源需求如下:

threads_per_block_X = 256; // 线程块中的线程数

shared_memory_per_block = 16 * 1024; // 每个块需要的共享内存 (16KB)

registers_per_thread = 32; // 每个线程需要的寄存器数

// 计算每个线程块需要的总寄存器数

registers_per_block = threads_per_block_X * registers_per_thread;

// registers_per_block = 256 * 32 = 8192 个寄存器

//---------------------------------------------------------------------

// 分析一个SM能同时运行多少个这样的线程块 (Block_Occupancy_Analysis)

//---------------------------------------------------------------------

// 1. 基于最大线程数的限制

// 一个SM最多容纳 MAX_THREADS_PER_SM 个线程。

// 每个块有 threads_per_block_X 个线程。

// 因此,基于线程数,SM最多容纳的块数 = MAX_THREADS_PER_SM / threads_per_block_X

// blocks_limit_by_threads = 2048 / 256 = 8 个块

// 中文解释:SM总共能跑2048个线程,我们的每个块有256个线程,所以光看线程数,最多能同时跑 2048/256 = 8个块。

// 2. 基于共享内存的限制

// 一个SM有 SHARED_MEMORY_PER_SM 的共享内存。

// 每个块需要 shared_memory_per_block 的共享内存。

// 因此,基于共享内存,SM最多容纳的块数 = SHARED_MEMORY_PER_SM / shared_memory_per_block

// blocks_limit_by_smem = (96 * 1024) / (16 * 1024) = 96KB / 16KB = 6 个块

// 中文解释:SM总共有96KB共享内存,我们的每个块要用16KB,所以光看共享内存,最多能同时跑 96/16 = 6个块。

// 3. 基于寄存器的限制

// 一个SM有 REGISTERS_PER_SM 个寄存器。

// 每个块需要 registers_per_block 个寄存器。

// 因此,基于寄存器,SM最多容纳的块数 = REGISTERS_PER_SM / registers_per_block

// blocks_limit_by_regs = (64 * 1024) / 8192 = 65536 / 8192 = 8 个块

// 中文解释:SM总共有65536个寄存器,我们的每个块要用8192个,所以光看寄存器,最多能同时跑 65536/8192 = 8个块。

// 4. 同时还要考虑SM本身支持的最大并发块数

// blocks_limit_by_hw_max = MAX_BLOCKS_PER_SM = 32 个块 (假设硬件直接限制)

// 中文解释:硬件本身可能还有一个顶格限制,比如这个SM设计上最多就同时跑32个块,不管你资源用得多么省。

// 实际一个SM能并发运行的该类型线程块的数量 (Occupancy per SM)

// 取上述所有限制中的最小值。

actual_concurrent_blocks_per_sm = min(

blocks_limit_by_threads,

blocks_limit_by_smem,

blocks_limit_by_regs,

blocks_limit_by_hw_max

);

// actual_concurrent_blocks_per_sm = min(8, 6, 8, 32) = 6 个块

// 中文解释:综合考虑线程数、共享内存、寄存器以及硬件直接限制,我们的Kernel在这个SM上,最多只能同时有6个线程块在运行。

// 计算SM的占用率 (Occupancy)

// 理论上SM能支持的最大线程数是MAX_THREADS_PER_SM

// 实际并发的线程数是 actual_concurrent_blocks_per_sm * threads_per_block_X

actual_concurrent_threads = actual_concurrent_blocks_per_sm * threads_per_block_X;

// actual_concurrent_threads = 6 * 256 = 1536 个线程

// 占用率 = 实际并发线程数 / SM最大并发线程数

occupancy = (float)actual_concurrent_threads / MAX_THREADS_PER_SM;

// occupancy = 1536 / 2048 = 0.75 (即 75%)

// 中文解释:这意味着在这种配置下,该SM的理论线程容量被利用了75%。

// 占用率是衡量GPU利用率的一个重要指标,但并非越高越好。

// 有时较低的占用率但每个线程工作更有效率,或者能更好利用其他资源(如内存带宽),可能整体性能更佳。

// 但通常来说,过低的占用率(例如只有一个块在SM上运行)意味着SM的大部分计算资源被浪费了,

// 因为没有足够的Warp来隐藏延迟。

// 打印结果 (概念性)

print("每个线程块需要的寄存器数量: ", registers_per_block);

print("基于线程数限制的并发块数: ", blocks_limit_by_threads);

print("基于共享内存限制的并发块数: ", blocks_limit_by_smem);

print("基于寄存器限制的并发块数: ", blocks_limit_by_regs);

print("SM硬件最大并发块数限制: ", blocks_limit_by_hw_max);

print("实际每个SM可并发的线程块数量: ", actual_concurrent_blocks_per_sm);

print("实际每个SM并发的线程数量: ", actual_concurrent_threads);

print("SM的理论占用率: ", occupancy * 100, "%");

/*

代码解释:

上述伪代码演示了在设计CUDA Kernel时,如何根据SM的硬件资源(总线程容量、总共享内存、总寄存器数)以及Kernel自身对每个线程块的资源需求(块内线程数、每块共享内存使用量、每线程寄存器使用量),来估算一个SM能够同时激活和运行多少个这样的线程块。

这个估算过程通常称为“占用率分析”(Occupancy Analysis)。

1. `MAX_THREADS_PER_SM`, `MAX_BLOCKS_PER_SM`, `SHARED_MEMORY_PER_SM`, `REGISTERS_PER_SM`: 这些是特定GPU架构下SM的硬件规格参数,可以从NVIDIA的官方文档或通过CUDA API查询得到。

2. `threads_per_block_X`, `shared_memory_per_block`, `registers_per_thread`: 这些是程序员在设计Kernel时确定的参数,或者是编译器编译Kernel后报告的资源使用情况。

3. `registers_per_block`: 计算得到每个线程块总共需要多少寄存器。

4. `blocks_limit_by_threads`, `blocks_limit_by_smem`, `blocks_limit_by_regs`: 分别从线程总数、共享内存总量、寄存器总量的角度计算SM最多能容纳多少个当前配置的线程块。计算方法都是用SM的总资源除以每个块消耗的该资源量。

5. `blocks_limit_by_hw_max`: SM硬件本身可能有一个最大并发块数的上限,独立于其他资源。

6. `actual_concurrent_blocks_per_sm`: 实际能在一个SM上并发运行的线程块数,是以上所有限制因素中的最小值。因为任何一个资源瓶颈都会限制并发块数。

7. `actual_concurrent_threads`: 根据实际并发块数和每块线程数,计算出SM上实际并发运行的总线程数。

8. `occupancy`: 用实际并发线程数除以SM理论上能支持的最大线程数,得到占用率。这个百分比反映了SM的线程调度能力被利用的程度。

这个分析非常重要,因为它直接关系到GPU的利用效率。如果占用率过低,意味着SM内部有很多Warp槽位是空闲的,当活动的Warp因为等待内存等原因阻塞时,没有足够的其他Warp可以被调度上来执行计算,从而导致计算单元闲置,性能下降。

NVIDIA提供了一个名为 "CUDA Occupancy Calculator" 的Excel电子表格工具,可以帮助开发者进行这种分析,并根据不同的GPU架构和Kernel参数调整,以期达到较好的占用率和性能。

在后续的Python CUDA编程中,虽然底层的细节可能被库封装,但理解这个概念有助于我们选择合适的线程块大小、调整共享内存使用等,以间接影响和优化GPU的实际占用率。

*/

这个伪代码示例虽然简单,但它点明了SM资源对于并行任务调度的硬性约束。在实际编程中,开发者需要已关注Kernel的资源消耗,并尝试调整参数(如线程块大小)来在不同的约束之间找到一个平衡点,以期获得较高的SM占用率,从而更好地隐藏延迟,提升GPU的整体计算效率。我们将在后续章节中看到,这些硬件层面的考量如何影响CUDA编程模型中的设计选择。

接下来,我们将继续深入探讨SM中的另一个关键组成部分:CUDA核心本身。

2.1.3 CUDA核心 (Scalar Processor/SP):单精度与双精度计算能力

CUDA核心,通常也被称为标量处理器(Scalar Processor, SP)或流处理器(Streaming Processor,尤其在早期的文献和AMD的语境中),是NVIDIA GPU内部执行算术和逻辑运算的最基本单元。它们是构成流式多处理器(SM)“计算火力”的基础。理解CUDA核心的特性,特别是其在单精度(FP32)和双精度(FP64)浮点运算方面的能力,对于评估GPU的理论性能和选择合适的GPU进行特定计算任务至关重要。

CUDA核心的基本功能:

每个CUDA核心本质上是一个算术逻辑单元(ALU),能够执行:

整数运算:如加法、减法、乘法、位运算(AND, OR, XOR, SHIFT)等。现代GPU对32位整数运算的支持已经非常成熟。

单精度浮点运算 (FP32):即符合IEEE 754标准的32位浮点数运算,包括加、减、乘、乘加(Fused Multiply-Add, FMA)等。FP32是GPU进行图形渲染和许多通用计算(包括深度学习训练的某些阶段和推理)时最常用的数据类型。FMA操作(a*b + c)尤其重要,因为它能在一个指令周期内完成两次浮点运算(一次乘法和一次加法),并且只进行一次舍入,从而提高精度和性能。现代GPU的CUDA核心通常都具备高效的FMA能力。

逻辑运算:比较、条件判断等。

CUDA核心的设计哲学是“小而多”。与CPU核心追求复杂的指令级并行(ILP)、乱序执行、分支预测等以加速单个线程的执行速度不同,GPU的CUDA核心设计相对简单,专注于高效地执行大量并行线程中的简单指令。通过集成成百上千个这样的核心,GPU实现了极高的并行处理吞吐量。

单精度浮点性能 (FP32 Performance):

GPU的单精度浮点性能是衡量其计算能力的一个关键指标,通常以每秒执行的浮点操作次数(FLOPS)来表示,单位是GFLOPS(每秒十亿次浮点运算)或TFLOPS(每秒万亿次浮点运算)。

一个GPU的总FP32理论峰值性能可以通过以下公式粗略估算:

FP32 TFLOPS = (SM数量) * (每个SM的FP32 CUDA核心数量) * (核心时钟频率 GHz) * (每个核心每个时钟周期执行的FP32操作数,对于FMA通常是2)

例如,如果一个GPU有80个SM,每个SM有64个FP32 CUDA核心,核心时钟频率为1.5 GHz,并且每个核心支持FMA(即每个周期2个FP32操作):

FP32 TFLOPS = 80 * 64 * 1.5 * 2 = 15360 GFLOPS = 15.36 TFLOPS

这个数值是理论峰值,实际应用中由于内存带宽限制、算法并行度、分支分化、数据依赖等多种因素,很难达到100%的理论峰值。然而,它仍然是比较不同GPU计算潜力的一个重要参考。

单精度计算在以下领域应用广泛:

计算机图形学:绝大多数实时渲染任务使用FP32。

深度学习:许多模型的训练(尤其是在混合精度训练中FP32作为累加精度)和推理主要依赖FP32或更低精度。

信号处理、图像视频处理:这些领域通常对精度要求不高,FP32足以满足需求且性能更优。

部分科学计算和模拟:当问题对数值精度要求不是极端苛刻时,FP32可以提供比FP64更快的计算速度。

双精度浮点性能 (FP64 Performance):

双精度浮点数(FP64)提供比单精度更高的数值精度(约15-17位十进制有效数字,而FP32约为7位)。这对于许多科学计算、工程模拟、金融建模等领域至关重要,因为这些应用中数值误差的累积可能导致结果的显著偏差。

然而,在GPU架构中,双精度计算单元的实现通常比单精度单元更复杂,占用更多的芯片面积和功耗。因此,NVIDIA对不同市场定位的GPU产品,其FP64性能配置有显著差异:

消费级GPU (如GeForce系列):这类GPU主要面向游戏和主流计算市场。为了控制成本和功耗,其FP64性能通常被大幅削减。例如,FP64的计算吞吐量可能是FP32的1/16、1/32甚至1/64。这意味着,尽管它们的FP32性能可能很高,但在需要高精度双精度计算的场景下表现不佳。

专业级GPU (如NVIDIA RTX Ada Generation Workstation GPUs, 先前的Quadro系列):这类GPU面向专业图形工作站、内容创作等领域。它们通常提供比消费级GPU更好的FP64性能,但仍可能低于其FP32性能的一定比例(例如1/2, 1/4, 或1/8)。

数据中心/HPC GPU (如NVIDIA Tesla/Hopper/Grace Hopper Superchip系列):这类GPU专为高性能计算和大规模AI训练而设计。它们通常配备了比例更高的FP64计算单元,其FP64性能可以达到FP32性能的1/2或1/3,甚至在某些专门针对HPC的型号中接近1:1(虽然较少见)。这是因为科学计算领域对双精度能力有强烈的需求。

一个SM内部可能包含专门的FP64单元,或者通过多个FP32单元组合(例如,两个FP32单元协同工作)来执行一个FP64操作,后者会导致FP64吞吐量降低。

估算FP64理论峰值性能的方法与FP32类似,只是需要将公式中的“每个SM的FP32 CUDA核心数量”替换为“每个SM的FP64计算单元等效数量”,并考虑其FMA能力。

为何已关注FP32与FP64的比例?

对于开发者而言,了解目标GPU的FP32和FP64性能及其比例非常重要:

算法选择:如果应用对精度要求不高,应优先考虑使用FP32,以获得更高的性能。

GPU选型:如果应用强依赖于双精度计算(如某些类型的物理模拟、有限元分析、高精度金融计算),则必须选择FP64性能强劲的数据中心级或特定专业级GPU。使用消费级GPU运行此类应用可能会导致计算时间过长,甚至结果不可接受。

混合精度计算:在深度学习等领域,混合精度技术(同时使用FP16、BF16进行存储和大部分计算,用FP32进行累加和权重更新)变得越来越流行。这需要GPU对不同精度都有良好的支持,尤其是张量核心的引入,极大地加速了FP16等低精度运算。即使在这种情况下,FP32的累加精度和速度仍然重要。

NVIDIA GPU架构中FP32/FP64核心的演进:

早期架构 (如Tesla G80/G92/GT200):开始引入GPGPU概念,GT200(如Tesla C1060, GTX 280)相对较早地提供了不错的FP64支持(FP64是FP32的1/8)。

Fermi架构 (如Tesla M2050/M2090, GeForce GTX 480/580):Fermi是NVIDIA首个重点已关注HPC的架构,显著增强了FP64性能,其FP64单元数量达到了FP32单元数量的一半(即FP64性能为FP32的1/2)。这使得Fermi在科学计算领域取得了巨大成功。

Kepler架构 (如Tesla K20/K40/K80, GeForce GTX 680/780/Titan):Kepler架构在消费级GPU (GK104/GK110-部分型号)中大幅削减了FP64单元(如1/24或1/8的FP32),但在其HPC版本 (GK110/GK210,如Tesla K20X/K40/K80) 中依然保持了较高的FP64与FP32的比例(通常是1/3)。

Maxwell架构 (如GeForce GTX 980, Titan X Maxwell):Maxwell主要已关注能效比和图形性能,其FP64性能相对于FP32非常低(通常是1/32)。

Pascal架构 (如Tesla P100, GeForce GTX 1080, Titan X Pascal):Pascal架构的GP100核心(用于Tesla P100)再次强调了HPC,提供了FP32一半的FP64性能。而消费级的GP102/GP104核心(用于GeForce和部分Quadro)的FP64性能仍然较低(1/32)。

Volta架构 (如Tesla V100, Titan V):Volta的GV100核心是HPC和AI的里程碑,FP64性能是FP32的一半,并且首次引入了张量核心。

Turing架构 (如GeForce RTX 2080, Quadro RTX系列, Tesla T4):Turing主要增强了光线追踪(RT核心)和AI推理(张量核心的改进),其FP64性能相对于FP32仍然不高(例如消费级为1/32),但专业卡和数据中心卡会有所不同。

Ampere架构 (如NVIDIA A100, GeForce RTX 3080/3090):Ampere架构的A100 GPU(GA100核心)为数据中心设计,提供了强大的FP64性能(FP32的一半),并配备了第三代张量核心。消费级的GA102核心(RTX 30系列)的FP64性能依然是FP32的1/64。

Hopper架构 (如NVIDIA H100):Hopper架构的H100 GPU进一步提升了针对AI和HPC的性能,其FP64性能通常是FP32的1/3(对于传统的FP64 CUDA核心),并引入了支持FP8的第四代张量核心和Transformer引擎。

Ada Lovelace架构 (如GeForce RTX 4090, NVIDIA RTX 6000 Ada Generation): 主要面向游戏和专业图形,FP64性能相比FP32依然有较大差距(例如1/64),但FP32性能和光追、AI性能大幅提升。

代码示例:检查设备计算能力 (CUDA C++ 概念)

在实际的CUDA编程中(通常是C++层面),你可以查询设备的计算能力(Compute Capability)版本号,这个版本号间接反映了GPU的架构特性,包括FP64的支持情况。你也可以直接查询FP64核心数量或FP64性能与FP32性能的比例。

#include <cuda_runtime.h>

#include <stdio.h>

// 简单的错误检查宏

#define CUDA_CHECK(err) {

if (err != cudaSuccess) {

fprintf(stderr, "CUDA Error: %s at %s:%d

", cudaGetErrorString(err), __FILE__, __LINE__);

exit(EXIT_FAILURE);

}

}

int main() {

int deviceCount; // 用于存储检测到的CUDA设备数量

CUDA_CHECK(cudaGetDeviceCount(&deviceCount)); // 获取CUDA设备数量

// 中文解释:调用cudaGetDeviceCount函数,获取系统中支持CUDA的GPU数量,并将结果存入deviceCount变量。CUDA_CHECK用于检查API调用是否成功。

if (deviceCount == 0) {

printf("No CUDA-enabled devices found.

"); // 如果没有找到CUDA设备,则打印信息

// 中文解释:如果设备数量为0,说明没有可用的NVIDIA GPU,程序退出。

return 0;

}

printf("Found %d CUDA-enabled device(s):

", deviceCount); // 打印找到的设备数量

// 中文解释:打印检测到的GPU数量。

for (int dev = 0; dev < deviceCount; ++dev) {

cudaDeviceProp deviceProp; // 定义一个cudaDeviceProp结构体,用于存储设备属性

CUDA_CHECK(cudaGetDeviceProperties(&deviceProp, dev)); // 获取指定设备的属性

// 中文解释:对每个检测到的GPU,调用cudaGetDeviceProperties函数获取其详细属性,并存储在deviceProp结构体中。'dev'是设备的索引(从0开始)。

printf("

--- Device %d: %s ---

", dev, deviceProp.name); // 打印设备编号和设备名称

// 中文解释:打印当前正在查询的设备编号和它的型号名称。

printf(" Compute Capability: %d.%d

", deviceProp.major, deviceProp.minor); // 打印计算能力版本

// 中文解释:打印GPU的计算能力版本,例如7.5, 8.6等。主版本号(major)和次版本号(minor)共同决定了GPU的架构特性。

printf(" Total Global Memory: %.2f GB

", deviceProp.totalGlobalMem / (1024.0 * 1024.0 * 1024.0)); // 打印全局内存大小

// 中文解释:打印GPU的总全局内存大小,单位转换为GB。

printf(" Number of SMs: %d

", deviceProp.multiProcessorCount); // 打印SM数量

// 中文解释:打印GPU拥有的流式多处理器(SM)的数量。

// 估算FP32 CUDA核心数量 (注意: 这只是一个估算,实际核心数可能因架构而异)

// 不同计算能力版本的SM内核心数不同,这里用一个简化的查询

// 更准确的方式是查阅对应计算能力版本的官方文档

int coresPerSM = 0;

if (deviceProp.major == 2 && deviceProp.minor == 0) coresPerSM = 32; // Fermi GF100

else if (deviceProp.major == 2 && deviceProp.minor == 1) coresPerSM = 48; // Fermi GF10x/GF11x

else if (deviceProp.major == 3) coresPerSM = 192; // Kepler

else if (deviceProp.major == 5) coresPerSM = 128; // Maxwell

else if (deviceProp.major == 6) coresPerSM = 128; // Pascal (GP100 SM has 64, GP10x has 128, this is a simplification)

else if (deviceProp.major == 7) coresPerSM = 64; // Volta / Turing

else if (deviceProp.major == 8) coresPerSM = 128; // Ampere (GA100 SM has 64, GA10x has 128 FP32 units, some can be used for INT32)

// Ampere GA10x "FP32 cores" are often counted with INT32 path, effectively 64 FP32 specific + 64 shared

// For GA100 it's 64 FP32 cores per SM.

// For GA102/GA104 (e.g. RTX 30 series), each SM has 4 partitions, each partition has 16 FP32 CUDA Cores for FP32/INT32, plus 16 FP32 CUDA Cores for FP32 only.

// So, an SM in GA102/GA104 has 4 * (16+16) = 128 "FP32 units" in marketing speak if they mean units capable of FP32.

// More precisely, a GA102 SM has 4 processing blocks. Each has a warp scheduler, dispatch unit, 16 FP32 CUDA cores, 16 INT32 CUDA cores, 8 LD/ST units, 4 SFUs, and one Tensor Core (Gen3).

// The 16 INT32 cores can also execute FP32 instructions. So, per processing block, 16 dedicated FP32 + 16 (INT32 or FP32) = 32 FP32 capable. 4 blocks mean 128 FP32-capable cores per SM.

else if (deviceProp.major == 9) coresPerSM = 128; // Hopper (each SM has 128 FP32 cores) / Ada Lovelace (each SM has 128 FP32 cores)

else coresPerSM = 0; // Unknown or not easily generalized

if (coresPerSM > 0) {

printf(" Estimated FP32 CUDA Cores: %d (SMs) * %d (Cores/SM) = %d

",

deviceProp.multiProcessorCount, coresPerSM, deviceProp.multiProcessorCount * coresPerSM);

// 中文解释:根据估算的每个SM的核心数和SM总数,打印GPU理论上的FP32 CUDA核心总数。

// 这是一个非常粗略的估计,NVIDIA市场宣传的“CUDA核心数”有时计算方式复杂,此代码仅为示意。

} else {

printf(" Estimated FP32 CUDA Cores: N/A (Cannot determine for CC %d.%d without more specific data)

", deviceProp.major, deviceProp.minor);

// 中文解释:如果无法根据计算能力简单估算,则提示无法确定。

}

// 检查双精度支持和比例 (更可靠的方式)

// deviceProp.kernelExecTimeoutEnabled; // (This is not for FP64)

// 通常,FP64性能与FP32的比例是架构固定的。

// 例如,对于Compute Capability 8.0 (Ampere GA100): FP64 perf is 1/2 of FP32 perf.

// 对于Compute Capability 8.6 (Ampere GA102/GA104): FP64 perf is 1/64 of FP32 perf.

// 对于Compute Capability 9.0 (Hopper H100): FP64 perf is 1/3 of FP32 "CUDA core" TFLOPs (or 1/2 of FP32 TFLOPs if counting specific FP64 units).

// H100 has 2 FP64 units per SM partition, 4 partitions, so 8 FP64 units per SM. An H100 SM has 128 "FP32 Cores".

// So FP64 to FP32 core count ratio is 8/128 = 1/16 if counting cores. Performance ratio can differ due to FMA etc.

// A more direct (but still somewhat indirect) way is to look at attributes like `cudaDevAttrConcurrentManagedAccess`

// or check documentation for the specific device or compute capability.

// The `cudaDeviceGetAttribute` function can query specific attributes.

int एकीकृत; // variable for integrated GPU check

cudaDeviceGetAttribute(&integriert, cudaDevAttrIntegrated, dev); // Check if GPU is integrated

// 中文解释:检查GPU是否为集成GPU。对于集成GPU,其内存和性能特性可能与独立GPU不同。

if (deviceProp.major >= 2) {

// Fermi and later generally have some FP64 capability

// A common way to express FP64 capability is relative to FP32.

// This is highly dependent on the specific microarchitecture (e.g., GF100 vs GK110 vs GP100 vs GV100 vs GA100 vs GH100)

// There isn't a direct deviceProp field for "FP64_cores_count" that is universally comparable like multiProcessorCount.

// Often, marketing materials or architecture whitepapers state the FP64/FP32 TFLOPs ratio.

// For example:

// CC 2.0 (Fermi HPC): 1/2 FP32

// CC 3.5/3.7 (Kepler HPC): 1/3 FP32

// CC 3.0/3.2 (Kepler Consumer): 1/24 or 1/8 FP32

// CC 5.x (Maxwell): 1/32 FP32

// CC 6.0 (Pascal GP100): 1/2 FP32

// CC 6.1/6.2 (Pascal Consumer): 1/32 FP32

// CC 7.0 (Volta): 1/2 FP32

// CC 7.5 (Turing): 1/32 FP32 (for consumer), better for Quadro

// CC 8.0 (Ampere A100): 1/2 FP32

// CC 8.6 (Ampere Consumer): 1/64 FP32

// CC 8.7 (Ampere Workstation, e.g. RTX A6000): 1/32 FP32

// CC 8.9 (e.g. NVIDIA DRIVE Orin): varies, often lower for automotive.

// CC 9.0 (Hopper H100): marketed as high FP64, ratio to FP32 depends on how FP32 is counted. If FP32 uses all units, H100 SMs can do e.g. 60 TFLOPs FP32, 30 TFLOPs FP64 (1/2).

// CC 9.0a (Ada Lovelace RTX 40 series): 1/64 FP32

printf(" FP64 Capability: ");

if ((deviceProp.major == 2 && deviceProp.minor == 0) || // Fermi (e.g., C2050)

(deviceProp.major == 6 && deviceProp.minor == 0) || // Pascal P100

(deviceProp.major == 7 && deviceProp.minor == 0) || // Volta V100

(deviceProp.major == 8 && deviceProp.minor == 0)) // Ampere A100

{

printf("High (typically 1/2 of FP32 TFLOPs)

");

// 中文解释:对于这些计算能力版本(主要是数据中心/HPC卡),双精度性能通常是单精度TFLOPs的一半。

} else if ((deviceProp.major == 3 && (deviceProp.minor == 5 || deviceProp.minor == 7)) ) {

// Kepler K20/K40/K80

printf("Good (typically 1/3 of FP32 TFLOPs)

");

// 中文解释:对于Kepler架构的HPC卡,双精度性能通常是单精度TFLOPs的三分之一。

} else if ((deviceProp.major == 8 && deviceProp.minor == 7)) {

// Ampere Workstation (e.g. RTX Axxxx)

printf("Moderate (typically 1/32 of FP32 TFLOPs for RTX A series)

");

}

else if (deviceProp.major == 9 && deviceProp.minor == 0) {

// Hopper H100

printf("Very High (strong FP64 performance, e.g., 1/2 of FP32 TFLOPs or better by some metrics)

");

}

else {

// Consumer cards or others with lower FP64

printf("Low (typically 1/16, 1/32, 1/64 or less of FP32 TFLOPs for consumer GPUs)

");

// 中文解释:对于其他大多数消费级GPU,双精度性能显著低于单精度,可能是1/16, 1/32, 1/64甚至更低。

}

} else {

printf(" FP64 Capability: Likely N/A or very limited (Pre-Fermi)

");

// 中文解释:对于Fermi之前的GPU,双精度能力通常不被强调或非常有限。

}

printf(" Clock Rate: %.2f GHz

", deviceProp.clockRate / (1000.0 * 1000.0)); // 打印核心时钟频率

// 中文解释:打印GPU的核心时钟频率,单位转换为GHz。

}

return 0;

}

/*

代码解释:

这个C++程序使用了CUDA Runtime API来查询系统中NVIDIA GPU的属性。

1. `cudaGetDeviceCount(&deviceCount)`: 获取可用的CUDA设备数量。

2. 循环遍历每个设备 (`for (int dev = 0; dev < deviceCount; ++dev)`).

3. `cudaGetDeviceProperties(&deviceProp, dev)`: 获取索引为 `dev` 的设备的属性,并将其存储在 `cudaDeviceProp` 结构体 `deviceProp` 中。

4. `deviceProp.name`: GPU的型号名称 (例如 "NVIDIA GeForce RTX 4090", "NVIDIA A100-SXM4-80GB")。

5. `deviceProp.major`, `deviceProp.minor`: 计算能力 (Compute Capability) 的主版本号和次版本号。这是判断GPU架构和特性的重要依据。

6. `deviceProp.totalGlobalMem`: GPU的总全局内存大小(以字节为单位)。

7. `deviceProp.multiProcessorCount`: GPU拥有的流式多处理器 (SM) 的数量。

8. 估算FP32 CUDA核心数: 这部分代码尝试根据计算能力版本来估算每个SM的CUDA核心数,然后乘以SM总数得到GPU的总核心数。这是一个简化和粗略的估计,因为“CUDA核心”的定义和计数方式在不同代NVIDIA GPU的市场宣传中可能有所不同,且实际微架构细节复杂。例如,Ampere架构的消费级GPU和数据中心级GPU的SM内部结构和FP32单元配置就有差异。最准确的信息应参考NVIDIA官方的架构白皮书或规格说明。

9. 判断FP64能力: `cudaDeviceProp` 结构体本身没有直接给出“FP64核心数”或精确的FP64/FP32性能比率的字段。因此,代码基于已知的不同计算能力版本(特别是区分HPC/数据中心卡与消费卡)的典型FP64性能特征(相对于FP32的比例)进行了一个概括性的判断。例如,`deviceProp.major == 8 && deviceProp.minor == 0` (如A100) 通常意味着强大的FP64能力 (FP32的1/2),而 `deviceProp.major == 8 && deviceProp.minor == 6` (如RTX 30系列消费卡) 则FP64能力很弱 (FP32的1/64)。`cudaDeviceGetAttribute` 可以用来查询更具体的属性,但也没有直接的FP64核心数字。

10. `deviceProp.clockRate`: GPU的核心时钟频率 (以kHz为单位)。

这个示例主要目的是展示如何通过编程方式获取GPU的一些基本硬件信息,并强调了理解计算能力版本和查阅官方文档对于准确评估GPU特性(包括FP32/FP64性能)的重要性。在Python中,像PyCUDA或Numba这样的库也会提供接口来访问这些设备属性,使得我们可以在Python脚本中进行类似的查询和判断。

*/

总结来说,CUDA核心是GPU执行计算的基石。GPU通过集成大量相对简单的CUDA核心来实现大规模并行。其在FP32和FP64计算能力上的配置差异,直接反映了GPU的市场定位和适用场景。开发者在选择GPU和优化CUDA程序时,必须充分考虑这些硬件特性。例如,如果你的Python CUDA程序需要高精度科学计算,那么选择一个FP64性能强劲的GPU并确保算法正确利用双精度数据类型至关重要。如果应用主要是深度学习推理或图形渲染,那么高FP32性能和(如果适用)强大的张量核心/RT核心能力将是更优先的考量。

2.1.4 GPU内存层次结构:速度、容量与访问模式的权衡

在2.1.2节中,我们讨论了流式多处理器(SM)作为GPU的计算核心,以及其中包含的CUDA核心、特殊功能单元等。然而,再强大的计算核心也需要数据。数据从哪里来?计算结果存到哪里去?数据传输的速度和效率如何?这些问题的答案都指向GPU的内存系统。

与CPU类似,GPU也采用了层次化的内存结构。这种设计是基于一个普遍的计算机体系结构原理:速度最快的存储器通常容量最小且成本最高,而容量最大的存储器通常速度最慢且成本较低。通过构建一个包含多种不同速度、容量和特性的内存类型的金字塔结构,系统可以在成本、容量和平均访问延迟之间取得平衡。

GPU的内存层次结构比典型的CPU系统更为复杂和特化,这主要是因为它需要满足大规模并行计算带来的极高的数据带宽需求和对低延迟访存的渴望。成千上万的线程同时运行,如果它们都频繁地等待从慢速内存中获取数据,那么GPU的计算单元将大部分时间处于空闲状态,并行计算的优势也就无从谈起。

下图是一个典型的NVIDIA GPU内存层次结构的示意图(请注意,具体细节可能因架构代次而异,但总体概念保持一致):

+-----------------------------------------------------------------------------+

| GPU |

| +-------------------------------------------------------------------------+ |

| | Device / Global Memory (GDDR/HBM) | | <-- Off-chip, Largest, Highest Latency

| | (DRAM) | |

| +----------------------------------^----------------------------------------+ |

| | L2 Cache (Shared by all SMs) | | <-- On-chip, Large, Medium Latency

| +----------------------------------^----------------------------------------+ |

| | SM 0 | SM 1 ... | |

| | +------------------------------+ | +------------------------------+ | |

| | | L1 Cache / Shared Memory | | | L1 Cache / Shared Memory | | | <-- On-chip, Fast, Per-SM

| | +--------------^---------------+ | +--------------^---------------+ | |

| | | CUDA Cores | Registers | | | CUDA Cores | Registers | | | <-- On-chip, Fastest, Per-Core/Thread

| | | (SP, SFU, | (Per Thread) | | | (SP, SFU, | (Per Thread) | | |

| | | Tensor Core)| | | | Tensor Core)| | | |

| | +--------------+---------------+ | +--------------+---------------+ | |

| | | Constant Cache (Per SM) | | | Constant Cache (Per SM) | | |

| | | Texture Cache (Per SM) | | | Texture Cache (Per SM) | | |

| | +------------------------------+ | +------------------------------+ | |

| +-------------------------------------------------------------------------+ |

+-----------------------------------------------------------------------------+

^ ^

| PCI Express Bus | (Potentially NVLink for multi-GPU)

v v

+-----------------------------------------------------------------------------+

| CPU Host System |

| +-------------------------------------------------------------------------+ |

| | Host Memory (System RAM) | |

| +-------------------------------------------------------------------------+ |

+-----------------------------------------------------------------------------+

(Local Memory is an abstraction for thread-private data that spills from registers

or for large thread-local arrays; it typically resides in off-chip Global Memory

but is accessed via L1/L2 caches if possible.)

图例解释:

箭头 (^, |) 表示数据访问路径或缓存层次。数据通常从较慢、较大容量的内存流向较快、较小容量的内存(或被其缓存)。

SM (Streaming Multiprocessor):GPU的计算单元集群。

CUDA Cores / Registers:每个SM内部有多个CUDA核心,每个核心(或更准确地说,每个线程)都有自己私有的寄存器。

L1 Cache / Shared Memory:每个SM内部拥有自己的L1缓存和共享内存。这两者在物理上可能共享同一块片上SRAM,但逻辑功能和管理方式不同。

Constant Cache / Texture Cache:每个SM通常也有专门用于常量内存和纹理内存访问的缓存。

L2 Cache:所有SM共享的二级缓存,位于全局内存和SM之间。

Device / Global Memory:GPU主要的板载显存,通常是GDDR或HBM类型。

Host Memory:CPU系统的主内存。

PCI Express Bus / NVLink:连接GPU和CPU主机系统,或在多GPU系统中连接GPU的总线。

现在,让我们逐一深入了解这些内存类型。

2.1.4.1 寄存器 (Registers)

位置与范围:寄存器位于SM的芯片上,直接集成在CUDA核心附近。它们是每个线程私有 (per-thread private) 的存储。这意味着一个线程不能访问另一个线程的寄存器。

速度与延迟:寄存器是GPU上速度最快的内存,访问延迟极低,通常只需要一个时钟周期。这使得它们成为存储频繁访问的局部变量、循环计数器和中间计算结果的理想场所。

容量:每个SM拥有一个总的寄存器文件 (Register File),这个文件由该SM上所有活动的线程共享。因此,每个线程可用的寄存器数量是有限的。这个限制因GPU架构而异(例如,一个SM可能有65536个32位寄存器,如果一个SM最多同时运行2048个线程,那么在理想情况下每个线程平均可以分到32个寄存器)。

编译器(如NVIDIA的NVCC)会尽力将内核函数(Kernel)中的变量分配到寄存器中。

如果一个线程请求的寄存器数量超过了硬件限制,或者SM上并发的线程数过多导致每个线程分配到的寄存器不足,就会发生寄存器溢出 (Register Spilling)。溢出的变量会被存储到速度慢得多的本地内存 (Local Memory) 中(实际上是全局内存的一部分)。寄存器溢出通常会对性能造成严重损害,因为对本地内存的访问延迟远高于寄存器。

可编程性:程序员不能直接指定某个变量必须存储在寄存器中(不像共享内存那样有显式声明)。变量是否分配到寄存器主要由编译器根据代码结构、变量作用域和生命周期以及可用的寄存器数量来决定。但是,程序员可以通过编写简洁的代码、限制局部变量的数量和生命周期、以及使用编译器选项(如--maxrregcount或__launch_bounds__)来间接影响寄存器的使用。

生命周期:寄存器中变量的生命周期通常与线程的生命周期相同,或者在其作用域内。

使用场景:

函数参数(如果数量不多)。

频繁读写的局部变量。

循环控制变量。

计算过程中的临时值。

对性能的影响与优化考量:

最小化寄存器使用:虽然寄存器很快,但过度使用会导致溢出。应避免在内核中定义不必要的大型局部数组或过多局部变量。

编译器优化:现代编译器在寄存器分配方面已经做得相当好。了解编译器的行为(例如,查看PTX汇编代码中.reg声明的数量)有助于理解寄存器压力。

启动边界 (__launch_bounds__):在CUDA C++中,可以通过__launch_bounds__(maxThreadsPerBlock, minBlocksPerMultiprocessor)来向编译器提供关于内核启动配置的提示。这可以帮助编译器在寄存器使用量和线程块在SM上的占用率(Occupancy)之间做出更好的权衡。如果指定了maxThreadsPerBlock,编译器会尝试优化内核,使得当每个块的线程数不超过此值时,寄存器使用量不会过高,从而允许SM上驻留更多的块(由minBlocksPerMultiprocessor暗示)。

占用率:SM上可用的总寄存器数量是固定的。如果每个线程使用较少的寄存器,那么SM就可以同时驻留更多的线程(来自更多的线程束Warp),从而提高占用率,这有助于隐藏内存访问延迟。反之,如果每个线程使用大量寄存器,SM能并发的线程数就会减少,可能导致占用率降低。

概念代码 (CUDA C++) – 寄存器使用

__global__ void register_example_kernel(float* in_data, float* out_data, int N) {

int idx = blockIdx.x * blockDim.x + threadIdx.x; // idx 可能会被分配到寄存器

// 中文解释:计算当前线程的全局索引,通常存储在寄存器中。

if (idx < N) {

float val = in_data[idx]; // val 可能会被分配到寄存器

// 中文解释:从全局内存读取一个值,并存入一个局部变量val,val很可能在寄存器中。

float temp_result = val * 2.0f; // temp_result 可能会被分配到寄存器

// 中文解释:对val进行计算,中间结果temp_result也可能在寄存器中。

// 更多复杂的计算,可能会使用更多的临时变量(潜在的寄存器)

for (int i = 0; i < 5; ++i) {

// 循环变量 i 通常在寄存器中

// 中文解释:循环计数器i几乎肯定在寄存器中。

temp_result = (temp_result + idx * 0.1f) * (1.0f - i * 0.05f);

// 中文解释:在循环内部进行一系列计算,这些计算产生的中间值如果频繁使用且生命周期短,编译器会优先考虑寄存器。

}

out_data[idx] = temp_result; // 将最终结果写回全局内存

// 中文解释:将计算得到的最终结果写回到全局内存。

}

}

// 编译时,NVCC编译器会分析此内核,并决定哪些变量(如idx, val, temp_result, i)

// 可以有效地放入寄存器中。如果内核非常复杂,或者循环展开导致大量临时变量,

// 就可能增加寄存器压力。

//

// 我们可以通过编译内核时使用 -Xptxas -v 选项 (或者 --ptxas-options=-v)

// 来查看PTX汇编信息,其中会报告每个线程使用的寄存器数量(通常表示为 "reg" 或 "registers")

// 以及其他资源的使用情况。

// 例如,编译命令可能像这样:

// nvcc -arch=sm_75 -Xptxas -v my_kernel.cu -o my_kernel_exec

// 输出中会包含类似:

// ptxas info : Compiling entry function '_Z25register_example_kernelPfS_i' for 'sm_75'

// ptxas info : Function properties for _Z25register_example_kernelPfS_i

// ptxas info : 0 bytes stack frame, 0 bytes spill stores, 0 bytes spill loads

// ptxas info : Used 16 registers, 352 bytes cmem[0] ... (示例输出)

// "Used 16 registers" 就表示这个内核的每个线程使用了16个寄存器。

// 如果看到 "spill stores" 或 "spill loads" 的数量非零,则表示发生了寄存器溢出。

/*

代码解释:

这个 `register_example_kernel` 函数是一个CUDA核函数。

- `idx`, `val`, `temp_result`, `i` 这些都是局部变量。

- 编译器 (NVCC) 在编译这个核函数时,会尝试将这些频繁使用的局部变量分配到GPU线程的私有寄存器中,因为寄存器访问速度最快。

- `idx` 用于存储线程的全局ID。

- `val` 用于从 `in_data` 读取数据。

- `temp_result` 用于存储中间计算结果。

- `i` 是循环计数器。

- 注释中提到了如何通过编译器选项查看实际的寄存器使用情况。如果编译器报告了 "spill stores" 或 "spill loads" 不为零,就意味着发生了寄存器溢出,部分变量被存入了较慢的本地内存,这通常需要优化代码以减少寄存器使用或调整启动参数。

- 理解这一点对于Python CUDA用户也很重要,因为像Numba这样的库在JIT编译Python函数为CUDA内核时,其底层的LLVM编译器也会进行类似的寄存器分配优化。虽然用户不直接写PTX,但代码的结构会影响最终的寄存器使用。

*/

寄存器是GPU上最宝贵的内存资源之一。高效地利用寄存器,同时避免溢出,是实现高性能CUDA内核的基础。

2.1.4.2 本地内存 (Local Memory)

本地内存是一个让初学者容易混淆的概念,因为它听起来像是某种快速的片上存储,但实际上并非如此。

本质与位置:本地内存实际上并不是一种特定类型的物理硬件内存。它是一个抽象概念,指的是那些虽然属于单个线程私有 (per-thread private),但不能被分配到寄存器中的数据所存储的位置。这些数据通常存储在片外的全局内存 (Device Memory / DRAM) 中。因此,本地内存的访问延迟和带宽特性与全局内存类似,即相对较慢。

触发条件:本地内存主要在以下两种情况下被使用:

寄存器溢出 (Register Spilling):当编译器发现一个线程需要的寄存器数量超过了可分配的上限时,它会将一部分“不太重要”或“不那么频繁访问”的变量从寄存器中“溢出”到本地内存。

大型线程私有数组 (Large Thread-Private Arrays or Structures):如果在内核中声明了一个较大的、仅由单个线程访问的数组或结构体,编译器也可能会将其直接分配在本地内存中,因为它太大而无法放入寄存器。例如 float private_array[128]; 这样的声明,如果这个数组确实是线程私有的,并且编译器确定它不会被优化掉或放入共享内存,那么它很可能在本地内存。

访问范围:与寄存器一样,本地内存中的数据也是线程私有的。一个线程不能访问另一个线程的本地内存。

生命周期:本地内存中变量的生命周期通常与线程的生命周期相同,或者在其声明的作用域内。

缓存:对本地内存的访问可以被L1缓存和L2缓存所利用(如果GPU架构支持并且缓存策略允许)。这意味着,如果对本地内存中的某个位置进行了重复访问,后续的访问可能会从缓存中命中,从而减少延迟。然而,首次访问或者不满足缓存条件的访问仍然会经历全局内存的高延迟。

可编程性:程序员通常不直接声明“使用本地内存”。本地内存的使用是编译器在寄存器分配不足或遇到大型线程私有数据结构时的自动行为。程序员能做的是通过编写代码来避免或减少对本地内存的依赖。

为何称为“本地”:尽管它物理上可能在全局内存,但从逻辑上讲,这些数据的作用域是“本地的”,即仅限于单个线程。

对性能的影响与优化考量:

性能陷阱:由于本地内存实际上是全局内存,其访问速度远慢于寄存器和共享内存。因此,大量的本地内存访问(尤其是由于寄存器溢出导致的)是CUDA程序性能不佳的常见原因。

识别本地内存使用:可以通过NVCC编译器的输出来检查本地内存的使用情况。在PTXAS的详细输出中(使用 -Xptxas -v 或 --ptxas-options=-v 编译选项),会报告所谓的 “lmem” 或 “stack frame” 的使用量,以及 “spill stores” 和 “spill loads” 的数量。非零的spill stores/loads明确指示了寄存器溢出。

例如,输出中可能会有类似 ptxas info : Used 16 registers, 64 bytes lmem 的信息,表明每个线程使用了64字节的本地内存。

减少本地内存使用:

优化寄存器使用:这是最直接的方法。减少不必要的局部变量,缩短变量生命周期,分解复杂表达式,避免在循环中不必要地声明大型数据结构。

使用共享内存:如果一个大型数据结构需要在线程块内的多个线程之间共享,或者即使是线程私有但可以通过分块处理并复用共享内存来减少对全局内存的直接访问,那么共享内存通常是更好的选择。

重新组织数据和算法:有时,算法或数据结构的根本改变可以显著减少对线程私有大块数据的需求。

检查编译器优化级别:确保使用适当的编译器优化级别(如 -O2 或 -O3),编译器可能会进行更积极的优化来减少寄存器压力。

概念代码 (CUDA C++) – 可能导致本地内存使用的示例

__global__ void local_memory_spill_example(float* out_data, int N) {

int idx = blockIdx.x * blockDim.x + threadIdx.x;

if (idx < N) {

// 假设我们有很多需要保持活跃的局部变量,以至于寄存器不够用

float r1, r2, r3, r4, r5, r6, r7, r8, r9, r10;

float r11, r12, r13, r14, r15, r16, r17, r18, r19, r20;

// ... 更多这样的变量 (这只是一个夸张的例子来说明问题)

r1 = idx * 1.0f; r2 = idx * 2.0f; /* ...以此类推,给它们都赋值... */

r20 = idx * 20.0f;

// 进行一些涉及到这些变量的复杂计算

float sum = r1 + r2 + r3 + r4 + r5 + r6 + r7 + r8 + r9 + r10 +

r11 + r12 + r13 + r14 + r15 + r16 + r17 + r18 + r19 + r20;

out_data[idx] = sum;

}

}

// 中文解释:在这个例子中,我们声明了大量的局部浮点变量 (r1 到 r20)。

// 如果这些变量都需要同时存在(编译器无法优化掉它们或重复使用寄存器),

// 并且总数超过了单个线程可用的寄存器数量,那么多余的变量就会被“溢出”到本地内存中。

// 对这些溢出变量的读写操作实际上是对全局内存的读写,会非常慢。

// 编译这个内核并查看PTXAS输出,很可能会看到非零的 "spill stores/loads"。

__global__ void local_memory_array_example(float* in_data, float* out_data, int N) {

int idx = blockIdx.x * blockDim.x + threadIdx.x;

if (idx < N) {

float private_buffer[256]; // 一个较大的线程私有数组

// 中文解释:这里声明了一个包含256个浮点数的线程私有数组 private_buffer。

// 这么大的数组 (256 * 4 bytes = 1KB) 几乎不可能完全放入寄存器。

// 编译器很可能会将其分配到本地内存(即线程栈上,物理位置在全局内存)。

// 从全局内存加载数据到这个私有缓冲区

for (int i = 0; i < 256; ++i) {

if (idx + i < N) {

// 边界检查

private_buffer[i] = in_data[idx + i];

// 中文解释:从全局内存 in_data 中读取数据,并存入 private_buffer。

// 这里的 private_buffer[i] 访问的是本地内存。

} else {

private_buffer[i] = 0.0f;

}

}

// 对私有缓冲区中的数据进行一些处理

float sum = 0.0f;

for (int i = 0; i < 256; ++i) {

sum += private_buffer[i] * private_buffer[i];

// 中文解释:对 private_buffer 中的数据进行计算。这些访问同样是本地内存访问。

}

out_data[idx] = sum;

}

}

// 中文解释:`local_memory_array_example` 内核中的 `private_buffer` 是一个大小为 256 的浮点数组。

// 如此大的线程局部数组通常无法完全放入寄存器,编译器会将其分配在本地内存中。

// 这意味着对 `private_buffer` 的所有读写操作实际上都是对(可能被缓存的)全局内存的访问。

// 如果这种访问模式不佳(例如,非合并访问,尽管对于私有数据合并性不是主要问题,但延迟是)

// 或者L1/L2缓存未命中,性能会受到很大影响。

// 在这种情况下,如果可能,应该考虑是否可以使用共享内存(如果数据可以在块内线程间共享或复用),

// 或者重新设计算法以避免大的线程私有临时数组。

/*

代码解释:

第一个内核 `local_memory_spill_example` 通过声明大量局部变量来模拟寄存器压力,可能导致寄存器溢出到本地内存。

第二个内核 `local_memory_array_example` 声明了一个较大的线程私有数组 `private_buffer`。这种数组因为体积太大,通常会被编译器直接分配在本地内存(逻辑上在线程的栈帧中,物理上在设备DRAM中)。对 `private_buffer` 的访问就会成为本地内存访问。

在实际编程中,应该通过编译器输出(如PTXAS的 `-v` 选项)来监控本地内存 (`lmem`) 的使用以及寄存器溢出 (`spill loads/stores`) 的情况。如果发现本地内存使用过多或有溢出,就需要仔细审查代码,尝试优化:

1. 减少局部变量的数量和作用域。

2. 如果数据可以在线程块内共享或被块内多个线程以某种模式处理,考虑使用共享内存。

3. 对于大型只读数据,如果访问模式合适,考虑常量内存或纹理内存。

4. 重新思考算法,看是否能以流式方式处理数据,或者分块处理,以减少每个线程需要同时维护的状态。

*/

总结一下,本地内存是性能优化的一个“雷区”。虽然它为编译器提供了一种处理寄存器不足或大型线程私有数据的方式,但过度依赖本地内存通常是性能瓶颈的标志。程序员应努力通过优化代码来最小化其使用。

2.1.4.3 共享内存 (Shared Memory)

共享内存是CUDA编程中进行性能优化的一个核心工具,它为线程块(Thread Block)内的线程提供了一个低延迟、高带宽的片上暂存区。

位置与范围:共享内存位于每个SM的芯片上 (on-chip)。它是由同一个线程块内的所有线程共享的 (per-block scope)。不同线程块之间的共享内存是相互独立的;一个线程块不能访问另一个线程块的共享内存。

速度与延迟:共享内存的访问速度远快于全局内存和本地内存,延迟非常低,几乎接近寄存器的访问速度(但通常比寄存器慢几个周期,具体取决于访问模式和架构)。其带宽也非常高。

容量:每个SM拥有一定总量的共享内存(例如,现代GPU可能是每个SM 48KB, 64KB, 96KB, 100KB, 128KB甚至更多,具体取决于GPU型号和配置)。这个总量由该SM上所有并发运行的线程块共同分配使用。

一个线程块可以请求使用的共享内存大小是有限制的(例如,单个块最多48KB或更高)。

内核启动时,如果声明的共享内存使用量加上其他资源需求(如寄存器)使得SM无法容纳足够的线程块以达到较好的占用率,性能也可能受影响。

可编程性:共享内存是由程序员显式声明和管理的。在CUDA C++中,使用 __shared__ 关键字在内核函数内部声明共享内存变量。在Python CUDA库(如Numba)中,也有相应的API(例如 cuda.shared.array())来声明共享内存数组。

生命周期:共享内存中变量的生命周期与线程块的生命周期相同。当线程块开始执行时,共享内存被分配;当线程块执行完毕后,其使用的共享内存被释放,可供其他线程块使用。块内线程对共享内存的修改对块内其他线程可见(需要适当的同步)。

Bank Conflicts (银行冲突):共享内存被组织成若干个等宽的存储体(Bank),通常是32个(对应一个Warp中的线程数),每个Bank在一个时钟周期内可以服务一个读或写请求。如果一个Warp内的多个线程同时访问同一个Bank中的不同地址,或者多个线程访问同一个Bank的同一个地址(广播是允许的,多个读到同一个地址没问题),这通常没问题。但是,如果一个Warp内的多个线程同时访问同一个Bank中的不同字地址 (different word addresses within the same bank),就会发生银行冲突。

发生银行冲突时,这些访问请求必须串行化处理,即需要多个时钟周期才能完成,从而降低了共享内存的有效带宽。例如,如果Warp中的k个线程访问了同一个Bank的不同字,那么这个访问就需要k个周期。

避免银行冲突是优化共享内存使用的关键之一。通常可以通过精心设计数据在共享内存中的布局(例如,添加padding)或调整访问模式来实现。对于宽度为4字节(如 float 或 int)的数据,如果一个Warp中线程 i 访问 shared_array[base + i],通常不会有冲突(因为地址和Bank索引通常是线性映射的)。但如果访问模式是 shared_array[base + k * threadIdx.x] (其中 k 恰好是Bank的数量或者其倍数),就可能导致严重的冲突。

同步:由于共享内存被块内所有线程共享,当一些线程写入共享内存,而另一些线程需要读取这些新写入的值时,必须进行同步,以确保写操作完成并且对所有线程可见。CUDA提供了 __syncthreads() 内置函数,它充当一个栅栏 (barrier),块内的所有线程都必须执行到 __syncthreads() 后,才能继续执行后续指令。这保证了在 __syncthreads() 之前的所有共享内存写操作对 __syncthreads() 之后的所有共享内存读操作都是可见的。

使用场景:共享内存的典型应用场景包括:

线程块内数据重用 (Data Reuse):当一块数据被线程块内的多个线程多次访问时,可以先将该数据从全局内存加载到共享内存,然后线程从共享内存中读取。这利用了共享内存的低延迟和高带宽,避免了多次高延迟的全局内存访问。这是许多并行算法(如矩阵乘法、卷积、FFT等)中的常见优化手段,通常称为“分块 (Tiling)”或“缓存分块 (Cache Tiling)”。

线程间协作与数据交换 (Inter-thread Communication):块内线程可以通过共享内存交换中间结果,实现更复杂的协作算法,例如并行归约 (Parallel Reduction)、直方图计算、扫描 (Scan) 等。

改进全局内存访问模式 (Improving Global Memory Access Patterns):有时,线程块内对全局内存的自然访问模式可能不是最优的(例如,非合并访问)。可以先以某种(可能是次优的)方式将数据读入共享内存,然后在共享内存中重新排列数据,再让线程以最优模式(例如,完全合并)从共享内存读取所需数据,或者以最优模式将计算结果写入共享内存,最后再从共享内存以合并方式写回全局内存。

对性能的影响与优化考量:

显著的性能提升潜力:合理使用共享内存是CUDA程序获得高性能的关键技术之一。

共享内存容量限制:SM上的共享内存总量是有限的。如果一个线程块请求过多的共享内存,可能会降低SM上可并发运行的线程块数量(即占用率),从而影响整体性能。需要在共享内存带来的访存优化与占用率之间找到平衡。

避免银行冲突:如前所述,仔细设计数据布局和访问模式至关重要。

正确使用同步:__syncthreads() 是保证数据一致性的必要手段,但它也是一个同步点,会强制Warp等待。滥用或不必要的 __syncthreads() 会引入开销。只在确实需要保证共享内存读写顺序时使用。

数据加载与计算的平衡:将数据从全局内存加载到共享内存本身也需要时间。如果数据只被使用一次,或者计算量相对于数据加载的开销非常小,那么使用共享内存可能得不偿失。

概念代码 (CUDA C++) – 使用共享内存进行分块矩阵乘法 (简化示例)

#define TILE_WIDTH 16 // 定义块的大小,通常与线程块的维度相关

__global__ void tiled_matrix_mul_kernel(const float* A, const float* B, float* C, int M, int N, int K) {

// A: M x K, B: K x N, C: M x N

// 声明共享内存用于存放A的子块 (tile_A) 和B的子块 (tile_B)

__shared__ float tile_A[TILE_WIDTH][TILE_WIDTH]; // 存储A的一个TILE_WIDTH x TILE_WIDTH的子块

// 中文解释:声明一个名为tile_A的二维共享内存数组,大小为TILE_WIDTH x TILE_WIDTH,用于暂存矩阵A的一个分块。

__shared__ float tile_B[TILE_WIDTH][TILE_WIDTH]; // 存储B的一个TILE_WIDTH x TILE_WIDTH的子块

// 中文解释:声明一个名为tile_B的二维共享内存数组,大小为TILE_WIDTH x TILE_WIDTH,用于暂存矩阵B的一个分块。

int tx = threadIdx.x; // 线程在块内的x方向索引 (0 to TILE_WIDTH-1)

// 中文解释:获取当前线程在线程块内的x方向索引。

int ty = threadIdx.y; // 线程在块内的y方向索引 (0 to TILE_WIDTH-1)

// 中文解释:获取当前线程在线程块内的y方向索引。

// 计算当前线程块负责计算的C矩阵子块的起始行和列

int row_C = blockIdx.y * TILE_WIDTH + ty; // C中目标元素的行

// 中文解释:计算当前线程负责计算的结果矩阵C中元素的行号。

int col_C = blockIdx.x * TILE_WIDTH + tx; // C中目标元素的列

// 中文解释:计算当前线程负责计算的结果矩阵C中元素的列号。

float C_value = 0.0f; // 用于累加C[row_C][col_C]的值,存储在寄存器中

// 中文解释:初始化一个浮点变量C_value为0,它将用于累加C矩阵对应元素的值,这个变量很可能在寄存器中。

// 遍历A的行和B的列方向上的所有tile

for (int t = 0; t < (K + TILE_WIDTH - 1) / TILE_WIDTH; ++t) {

// t 是 tile的索引

// 中文解释:外层循环遍历所有需要的“瓦片”(tile)。矩阵A按列分块,矩阵B按行分块。

// (K + TILE_WIDTH - 1) / TILE_WIDTH 是一种向上取整的整数除法,计算沿K维度需要多少个tile。

// 1. 从全局内存加载数据到共享内存 tile_A 和 tile_B

// 每个线程负责加载tile_A中的一个元素和tile_B中的一个元素

// 加载 tile_A 的元素

int row_A_load = blockIdx.y * TILE_WIDTH + ty;

int col_A_load = t * TILE_WIDTH + tx;

if (row_A_load < M && col_A_load < K) {

tile_A[ty][tx] = A[row_A_load * K + col_A_load];

// 中文解释:当前线程负责从全局内存A中加载一个元素到共享内存tile_A的相应位置。

// 注意这里的索引映射:线程(ty, tx)加载到tile_A[ty][tx]。

// 边界检查 (row_A_load < M && col_A_load < K) 是必须的,防止越界访问。

} else {

tile_A[ty][tx] = 0.0f; // Padding with 0 if out of bounds

// 中文解释:如果越界,则用0填充共享内存,避免影响计算结果。

}

// 加载 tile_B 的元素

int row_B_load = t * TILE_WIDTH + ty;

int col_B_load = blockIdx.x * TILE_WIDTH + tx;

if (row_B_load < K && col_B_load < N) {

tile_B[ty][tx] = B[row_B_load * N + col_B_load];

// 中文解释:当前线程负责从全局内存B中加载一个元素到共享内存tile_B的相应位置。

// 注意这里的索引映射:线程(ty, tx)加载到tile_B[ty][tx]。

// 同样需要边界检查。

} else {

tile_B[ty][tx] = 0.0f; // Padding with 0 if out of bounds

// 中文解释:如果越界,则用0填充。

}

__syncthreads(); // 同步线程块内所有线程

// 中文解释:确保所有线程都已经完成了从全局内存到共享内存的数据加载,

// tile_A 和 tile_B 中的数据对块内所有线程都可见且是最新的。

// 2. 从共享内存进行计算

// 每个线程计算C_value的部分和

for (int i = 0; i < TILE_WIDTH; ++i) {

C_value += tile_A[ty][i] * tile_B[i][tx];

// 中文解释:内层循环。每个线程从共享内存tile_A和tile_B中读取数据,

// 并进行乘加运算,累加到自己的私有变量C_value中。

// tile_A[ty][i] 表示A子块的第ty行第i列。

// tile_B[i][tx] 表示B子块的第i行第tx列。

// 这种访问模式 (行访问tile_A, 列访问tile_B) 是矩阵乘法的标准做法。

// 由于数据在共享内存中,这里的访问速度非常快。

}

__syncthreads(); // 再次同步(重要!)

// 中文解释:确保当前tile的所有计算都已完成,并且所有对C_value的累加(如果C_value本身也在共享内存中,虽然这里不是)

// 或者对共享内存的潜在修改(如果算法更复杂)都已经完成,

// 然后才能进入下一个外层循环去加载下一个tile的数据到共享内存。

// 如果不加这个同步,下一个tile的数据可能会覆盖正在被其他线程读取的上一个tile的数据。

}

// 3. 将最终结果写回全局内存C

if (row_C < M && col_C < N) {

C[row_C * N + col_C] = C_value;

// 中文解释:将当前线程计算得到的C矩阵元素值C_value写回到全局内存C的相应位置。

// 同样需要边界检查。

}

}

/*

main函数中如何启动这个kernel (概念性):

int main() {

// ... 初始化矩阵 A, B, C_gpu (在GPU上分配内存) ...

// ... 将 A, B 从CPU拷贝到GPU ...

dim3 threadsPerBlock(TILE_WIDTH, TILE_WIDTH); // 每个块有 TILE_WIDTH x TILE_WIDTH 个线程

// 中文解释:定义线程块的维度,这里是TILE_WIDTH x TILE_WIDTH。

dim3 numBlocks((N + TILE_WIDTH - 1) / TILE_WIDTH, (M + TILE_WIDTH - 1) / TILE_WIDTH); // 计算需要的块数

// 中文解释:计算网格(Grid)的维度,即需要多少个线程块来覆盖整个输出矩阵C。

// M是C的行数,N是C的列数。

// 共享内存大小计算:

// size_t shared_mem_size = 2 * TILE_WIDTH * TILE_WIDTH * sizeof(float);

// 这个大小通常不需要在启动时显式指定,因为 `__shared__` 变量的大小是编译时确定的。

// 如果是动态共享内存,才需要在kernel启动时作为第三个参数传入。

tiled_matrix_mul_kernel<<<numBlocks, threadsPerBlock>>>(A_gpu, B_gpu, C_gpu, M, N, K);

// 中文解释:以计算出的numBlocks和threadsPerBlock配置启动核函数。

// CUDA_CHECK(cudaGetLastError());

// CUDA_CHECK(cudaDeviceSynchronize());

// ... 将 C_gpu 从GPU拷贝回CPU ...

// ... 清理资源 ...

return 0;

}

*/

/*

代码解释:

这是一个使用共享内存进行优化的分块矩阵乘法核函数 (`tiled_matrix_mul_kernel`) 的简化示例。

基本思想是:

1. **分块 (Tiling)**:将大的输入矩阵A和B以及输出矩阵C逻辑上划分为许多小的子矩阵(称为tile或块),每个子矩阵的大小为 `TILE_WIDTH x TILE_WIDTH`。

2. **线程块处理子矩阵**:每个CUDA线程块负责计算C的一个子矩阵。块内的每个线程负责计算该C子矩阵中的一个元素。

3. **共享内存加载**:

* 在计算C的一个子矩阵时,会涉及到A的多个行子块和B的多个列子块。

* 在主循环(`for (int t = ...)`)的每次迭代中,线程块内的所有线程协同地从全局内存中将当前需要的A的一个子块加载到共享内存 `tile_A`,将B的一个子块加载到共享内存 `tile_B`。

* 例如,`tile_A[ty][tx] = A[...]` 这行代码中,块内的每个线程 (`threadIdx.y`, `threadIdx.x`) 并行地从全局内存A中读取一个元素,并存入其在共享内存 `tile_A` 中的对应位置。

4. **同步 (`__syncthreads()`)**:在所有线程都将数据加载到 `tile_A` 和 `tile_B` 之后,必须调用 `__syncthreads()`。这确保了共享内存中的数据对块内所有线程都是完整和可见的,然后才能进行下一步的计算。

5. **共享内存计算**:一旦数据加载到共享内存,块内每个线程就从 `tile_A` 和 `tile_B` 中读取数据,进行乘法和累加运算,以计算其负责的C矩阵元素的(部分)值。由于共享内存访问速度远快于全局内存,这一步的计算效率很高。

* `C_value += tile_A[ty][i] * tile_B[i][tx];` 这一行是核心计算。每个线程都执行 `TILE_WIDTH` 次这样的乘加操作,利用共享内存中的数据。

6. **再次同步**:在内层计算循环(`for (int i = ...)`)之后,以及在下一次外层循环(加载下一个tile)之前,通常也需要 `__syncthreads()`。这确保了当前tile的所有计算都完成,并且所有线程都结束了对当前共享内存内容的读取,然后才能安全地用下一个tile的数据覆盖共享内存。

7. **结果写回**:当外层循环结束(即C子矩阵的一个元素的所有部分和都已累加到 `C_value`),每个线程将其最终计算得到的 `C_value` 写回到全局内存C的相应位置。

**共享内存带来的好处**:

* **数据重用**:`tile_A` 中的每个元素被 `TILE_WIDTH` 个线程(同一行的线程)在内层计算循环中读取 `TILE_WIDTH` 次(如果考虑每个线程的内循环)。类似地,`tile_B` 中的每个元素也被 `TILE_WIDTH` 个线程(同一列的线程)读取。如果没有共享内存,这些重复的读取都需要访问慢速的全局内存。通过将tile加载到共享内存,这些重复访问都变成了快速的片上内存访问。

* **减少全局内存事务**:通过让线程块协同加载一个tile到共享内存,可以更好地组织对全局内存的访问,使其更倾向于合并访问(Coalesced Access),从而提高全局内存带宽的利用率。

**注意事项**:

* `TILE_WIDTH` 的选择很重要。它通常与线程块的维度(例如,`blockDim.x`, `blockDim.y`)相关,并且需要考虑SM的共享内存容量、寄存器使用、以及避免银行冲突等因素。通常选择16或32是常见的做法。

* 边界条件处理(`if (row_A_load < M && col_A_load < K)`等)非常重要,以防止对全局内存的越界访问,特别是在矩阵维度不能被`TILE_WIDTH`整除时。

* 这个例子为了简化,假设A、B、C都是二维的,并且以行主序存储。实际应用中可能更复杂。

* 银行冲突:在这个例子中,如果 `TILE_WIDTH` 是32,并且 `tile_A[ty][i]` 的访问(`ty`固定,`i`变化)和 `tile_B[i][tx]` 的访问(`i`变化,`tx`固定)通常不会有银行冲突,因为访问的是不同的行或列,或者对于`tile_A`是同一行内不同列,对于`tile_B`是同一列内不同行。更准确地说,只要Warp内的线程访问共享内存时,地址映射到不同的Bank,或者访问同一Bank的同一地址(广播),就不会冲突。这个例子中的访问模式一般是安全的。

共享内存是CUDA中一个强大的工具,但需要精心设计和使用才能发挥其最大效用。对于许多数据并行算法,利用共享内存实现分块处理是提升性能的关键步骤。在Python CUDA库中,如Numba的`@cuda.jit`装饰的内核里,可以使用`cuda.shared.array()`来创建共享内存数组,其使用逻辑和CUDA C++中的`__shared__`类似。

共享内存的正确和高效使用,往往是区分CUDA新手和有经验开发者的一个重要标志。它是挖掘GPU并行计算潜力的核心技术之一。

2.1.4.4 L1缓存 (L1 Cache)

L1缓存是位于每个流式多处理器(SM)内部的一小块高速片上存储器,它与共享内存在物理上可能共享同一块SRAM,但其功能定位和管理方式与共享内存有着显著的区别。L1缓存的主要目的是自动缓存对本地内存(Local Memory)和全局内存(Global Memory)的访问,以减少访问这些较慢内存的延迟,并可能提高有效带宽。

位置与范围:L1缓存位于每个SM的芯片上 (on-chip)。它是SM级别的资源,服务于该SM上运行的所有线程。

速度与延迟:L1缓存的访问速度快于全局内存和L2缓存,但通常略慢于共享内存(如果两者竞争同一物理SRAM资源,且共享内存的访问模式更优时)和寄存器。其延迟比直接访问全局内存要低得多。

容量:每个SM的L1缓存容量相对较小,通常与共享内存竞争同一物理SRAM。在NVIDIA的某些GPU架构中(例如Fermi, Kepler, Maxwell, Pascal架构的部分配置,以及更新架构中的某些模式),SM内部的片上存储(通常为64KB、96KB、128KB或更多)可以被动态地或静态地配置为不同比例的L1缓存和共享内存。

例如,一个SM可能有64KB的片上存储,可以配置为:

48KB 共享内存 + 16KB L1缓存

16KB 共享内存 + 48KB L1缓存

32KB 共享内存 + 32KB L1缓存 (某些架构可能不支持完全灵活的划分)

从Volta架构开始,L1缓存和共享内存的物理存储被分开了,L1数据缓存通常与纹理缓存单元(Texture Cache)结合,形成一个统一的L1纹理缓存(L1/Texture Cache),而共享内存则有其专用的物理存储空间。这种分离简化了资源管理,并可能带来性能上的好处,因为L1和共享内存的访问模式和需求不同。例如,Volta V100每个SM拥有128KB的L1数据缓存/共享内存,可以灵活配置。Ampere A100每个SM拥有高达192KB的L1数据缓存/共享内存组合容量。Hopper H100每个SM则有256KB的可配置L1数据缓存,并与一个统一的L2缓存协同工作。

可编程性:L1缓存对于程序员来说通常是透明的,由硬件自动管理。程序员不能像控制共享内存那样直接将数据放入L1缓存或从中读取。L1缓存的行为(缓存哪些数据、何时替换)由硬件的缓存策略(如LRU – Least Recently Used,最近最少使用算法)决定。

虽然不能直接控制,但程序员可以通过理解L1缓存的行为特性来间接影响其效率。例如,具有良好空间局部性(访问彼此靠近的内存地址)和时间局部性(在短时间内重复访问相同的内存地址)的全局/本地内存访问模式,更容易从L1缓存中受益。

缓存内容:

本地内存访问:对本地内存(即寄存器溢出或大型线程私有数组存储在全局内存中的部分)的访问通常会通过L1缓存。这是L1缓存的一个主要作用,以缓解本地内存访问的高延迟。

全局内存访问:默认情况下,在许多NVIDIA GPU架构中,对全局内存的访问可能会绕过L1缓存(bypass L1),直接进入L2缓存。这是因为全局内存的访问通常是流式的,或者对于所有SM来说是共享的,L1缓存容量有限,如果缓存所有全局内存访问,可能会导致缓存污染和效率低下。

然而,可以通过编译器指令或内联PTX汇编来**提示(hint)**某些全局内存访问应该尝试使用L1缓存。例如,在CUDA C++中,可以使用 ldg() 系列函数(如 __ldg()) 进行只读全局内存加载,这些加载通常会通过只读数据缓存(Read-Only Data Cache,在某些架构中与L1/纹理缓存紧密相关或就是一部分)进行缓存,从而提高重复读取的性能。

对于可读写的全局内存访问,也可以通过特定的编译器选项或ptx指令来改变其默认的缓存行为(例如,请求缓存到L1)。例如,volatile关键字可能会影响缓存行为,或者使用特定的cache-level修饰符(如在PTX中)。

缓存粒度 (Cache Line Size):L1缓存和L2缓存都以缓存行(Cache Line)为单位进行数据交换。缓存行的大小因架构而异,通常是32字节、64字节或128字节。当发生缓存未命中(Cache Miss)时,硬件会从下一级存储(L2缓存或全局内存)中加载整个缓存行到L1缓存。这意味着即使线程只需要缓存行中的一小部分数据,整个缓存行也会被加载。

理解缓存行对于优化全局内存访问非常重要。如果一个Warp中的线程访问的数据都位于同一个或少数几个缓存行内(即合并访问,Coalesced Access),那么只需要很少的内存事务就可以满足所有线程的需求,从而有效利用内存带宽并增加L1缓存的命中机会(如果数据被缓存)。

一致性 (Coherency):由于L1缓存是每个SM私有的,如果不同SM上的线程修改了全局内存中同一位置的数据,L1缓存的一致性问题就需要L2缓存或更底层的内存系统来处理。通常,GPU的缓存一致性模型比CPU的要弱一些,或者依赖于程序员使用正确的同步原语(如原子操作、volatile、内存栅栏、__threadfence()系列函数)来确保跨SM的数据可见性和一致性。对于只读数据,一致性问题较少。

L1缓存与共享内存的比较:

| 特性 | L1 缓存 (L1 Cache) | 共享内存 (Shared Memory) |

|---|---|---|

| 位置 | 片上,每个SM | 片上,每个SM |

| 范围 | SM级别(服务于SM内所有线程对全局/本地内存的访问) | 线程块级别(由块内所有线程共享) |

| 管理 | 硬件自动管理,对程序员透明 | 程序员显式声明、分配和管理 |

| 内容 | 缓存本地内存访问、部分全局内存访问(可提示) | 程序员显式加载的数据 |

| 容量 | 较小,可能与共享内存共享物理SRAM或有独立空间 | 较小,可配置,由SM上所有并发块共享总容量 |

| 延迟 | 低 | 非常低(通常优于L1,尤其在无银行冲突时) |

| 带宽 | 高 | 非常高 |

| 主要用途 | 减少对本地/全局内存的平均访问延迟,利用时空局部性 | 线程块内数据重用、线程间协作、优化全局内存访问模式 |

| 编程模型 | 隐式使用,通过优化访问模式间接影响 | 显式使用,需要仔细规划数据布局和同步 |

| 数据保证 | 不保证数据一定在缓存中 | 程序员控制数据的存在和生命周期(在块内) |

对性能的影响与优化考量:

利用数据局部性:编写具有良好空间局部性和时间局部性的代码,可以提高L1缓存的命中率。

空间局部性:访问彼此靠近的内存地址。例如,按行处理二维数组(如果按行存储)通常比按列处理具有更好的空间局部性。合并的全局内存访问是空间局部性的一个典型例子。

时间局部性:在短时间内重复访问相同的内存地址。如果某个数据项被多次使用,它更有可能保留在L1缓存中。

理解默认缓存策略:了解目标GPU架构对于全局内存访问的默认L1缓存策略(是默认缓存还是默认绕过)。如果默认绕过,而你的应用场景中某些全局内存数据具有良好的重用性,可以考虑使用 __ldg()(对于只读数据)或查阅文档看是否有其他方式提示L1缓存。

配置L1/共享内存比例(如果可配置):在允许配置L1和共享内存比例的旧架构上,需要根据内核的具体需求来权衡。如果内核大量使用共享内存,则分配更多空间给共享内存;如果内核对共享内存需求不高,但有较多随机或可缓存的全局/本地内存访问,则增加L1缓存可能更有益。NVIDIA提供了API(如 cudaFuncSetCacheConfig)来设置这种偏好(例如,cudaFuncCachePreferShared, cudaFuncCachePreferL1, cudaFuncCachePreferEqual)。

// CUDA C++ 示例: 设置函数缓存配置 (适用于可配置L1/共享内存的架构)

// cudaError_t cudaFuncSetCacheConfig(const void* func, enum cudaFuncCache cacheConfig);

// - func: 指向内核函数的指针 (e.g., my_kernel_function)

// - cacheConfig:

// - cudaFuncCachePreferNone: 不设置偏好 (使用设备默认)

// - cudaFuncCachePreferShared: 偏好更大的共享内存

// - cudaFuncCachePreferL1: 偏好更大的L1缓存

// - cudaFuncCachePreferEqual: 偏好均等分配 (如果硬件支持)

// 例如,在调用内核之前:

// CUDA_CHECK(cudaFuncSetCacheConfig(my_kernel, cudaFuncCachePreferL1));

// my_kernel<<<blocks, threads>>>(...);

// 中文解释:这行代码尝试告诉CUDA运行时,对于my_kernel函数,我们更希望SM将更多的片上SRAM用作L1缓存,而不是共享内存。

// 注意:这个API的效果取决于GPU架构。在L1和共享内存物理分离的现代架构(如Volta及之后),此API可能无效或行为不同。

// 需要查阅特定计算能力的文档。

对于Python CUDA(如Numba),这种底层的缓存配置可能不直接暴露给用户,或者由编译器根据启发式规则自动处理。

避免缓存颠簸 (Cache Thrashing):如果工作集(频繁访问的数据集合)的大小远超L1缓存容量,并且访问模式不佳,可能导致缓存中的数据被频繁换入换出,反而降低性能。这种情况下,可能需要重新设计算法或数据结构,或者更依赖于程序员控制的共享内存。

只读数据缓存 (__ldg):对于那些从全局内存加载后在内核中只读不写的数据,如果它们会被多次读取,使用 __ldg() (Load Global using L1/Texture Cache) 是一个很好的优化手段。__ldg() 保证加载操作至少通过只读数据缓存(通常与L1或纹理路径相关联),这对于具有良好时间局部性的只读数据访问模式非常有效。

// CUDA C++ 示例: 使用 __ldg()

__global__ void ldg_example_kernel(const float* __restrict__ read_only_global_data,

float* out_data,

int N,

int an_index) {

int idx = blockIdx.x * blockDim.x + threadIdx.x;

if (idx < N) {

// 假设 read_only_global_data[an_index] 是一个会被很多线程重复读取的值

// 或者一个线程内会多次读取它

float val;

// 使用 __ldg 来加载只读数据,提示通过只读缓存路径

// __ldg需要指向const __restrict__的指针

val = __ldg(&read_only_global_data[an_index]);

// 中文解释:使用__ldg函数从read_only_global_data数组的an_index位置加载一个浮点数。

// __ldg提示编译器和硬件,这个加载操作应该尝试通过只读数据缓存路径(通常是L1/纹理缓存的一部分),

// 这对于那些被多个线程或多次重复读取的只读数据尤其有效。

// 指针参数需要是 const float* __restrict__ 类型。

out_data[idx] = val * idx;

}

}

/*

代码解释:

`ldg_example_kernel` 中的 `__ldg(&read_only_global_data[an_index])` 调用是一个例子。

- `read_only_global_data` 必须是指向常量(`const`)且不与其他指针别名(`__restrict__`)的全局内存数据的指针。

- `__ldg()` 的目标是告诉硬件,这个加载操作最好通过为只读数据优化的缓存路径(例如L1的只读部分或纹理缓存)。

- 如果 `read_only_global_data[an_index]` 的值在内核执行期间不会改变,并且被当前SM上的多个线程(或同一个线程多次)访问,那么第一次访问可能会从全局内存加载并缓存它,后续的访问则可能从高速缓存中命中,从而显著提高性能。

- 这种机制对于查找表(lookup tables)或在计算中反复使用的不变参数非常有用。

- 在NVIDIA的Compute Capability 3.5及更高版本的GPU上支持 `__ldg()`。

- 对于Numba用户,Numba编译器可能会自动识别某些只读访问模式并进行类似的优化,或者提供特定的方式来指示这种访问,但这通常不如CUDA C++中直接使用 `__ldg()` 那样显式。

*/

本地内存与L1:由于本地内存访问(寄存器溢出)默认会通过L1缓存,因此即使发生了溢出,如果溢出的数据具有良好的时空局部性,L1缓存也能在一定程度上缓解其性能影响。但这绝不意味着可以忽视寄存器溢出,因为L1缓存的容量和带宽仍然是有限的,且首次访问的延迟依然存在。

L1缓存的演进与趋势:

随着GPU架构的发展,L1缓存的设计也在不断演进。

容量增加:每一代新GPU通常都会增加SM的片上存储总量,从而也可能增加L1缓存的可用容量。

功能分离与专门化:如前所述,从Volta开始,L1数据缓存与共享内存物理分离,并与纹理单元的缓存更紧密地集成。这允许两者独立优化和扩展。

更智能的缓存策略:硬件设计者不断改进缓存管理算法,以期在各种工作负载下都能获得更好的平均性能。

与L2缓存的协同:L1和L2缓存协同工作,形成一个更有效的多级缓存体系。

2.1.4.5 常量内存 (Constant Memory)

常量内存,顾名思义,是GPU上用于存储在内核执行期间不会改变的数据(即常量)的一块特殊内存区域。它具有专门的硬件支持,包括片上缓存,旨在优化对这些常量数据的访问。

位置与范围:

常量数据本身存储在设备内存(全局内存)中。一个GPU设备通常拥有几十KB到几MB的常量内存空间(例如,典型的是64KB,但这只是逻辑限制,物理存储在DRAM中)。

每个SM都拥有一个私有的片上常量缓存 (on-chip constant cache),用于缓存从设备内存中读取的常量数据。

速度与延迟:

当常量数据命中SM的常量缓存时,访问速度非常快,延迟极低,几乎可以与寄存器访问相媲美。带宽也非常高,因为常量缓存通常支持高效的广播机制。

如果常量数据未命中常量缓存(Cache Miss),则需要从设备内存中加载,此时的延迟会与全局内存访问类似,相对较高。但是,一旦加载到常量缓存,后续的访问就会非常快。

容量:

逻辑常量内存空间:GPU驱动程序和运行时为常量内存保留了一部分设备内存,通常是64KB。程序员通过特定方式声明的常量数据会存放在这个区域。

片上常量缓存:每个SM的常量缓存容量相对较小,例如几KB(如8KB或16KB)。这个缓存用于存放当前SM上活动线程最常访问的常量数据。

可编程性:

在CUDA C++中,使用 __constant__ 关键字在文件作用域(全局作用域,不能在函数内部)声明常量内存变量。

// CUDA C++ 示例: 声明常量内存

__constant__ float MY_CONSTANT_ARRAY[256];

__constant__ int MY_SCALAR_CONSTANT;

// 中文解释:

// MY_CONSTANT_ARRAY 是一个包含256个浮点数的数组,存储在常量内存中。

// MY_SCALAR_CONSTANT 是一个整型标量,也存储在常量内存中。

// 这些变量在编译时确定大小,其内容在运行时通过主机端API拷贝一次后,在内核执行期间不能被设备端代码修改。

常量内存中的数据必须在主机端 (CPU端) 通过 cudaMemcpyToSymbol() 函数进行初始化或更新。内核函数(设备端代码)只能读取常量内存,不能写入。

// CUDA C++ 示例: 从主机初始化常量内存

float host_array[256];

int host_scalar = 10;

// ... 初始化 host_array 和 host_scalar ...

// 将数据从主机内存拷贝到GPU上的常量内存

CUDA_CHECK(cudaMemcpyToSymbol(MY_CONSTANT_ARRAY, host_array, 256 * sizeof(float)));

// 中文解释:将主机上的host_array数组的内容拷贝到GPU上声明的__constant__变量MY_CONSTANT_ARRAY。

CUDA_CHECK(cudaMemcpyToSymbol(MY_SCALAR_CONSTANT, &host_scalar, sizeof(int)));

// 中文解释:将主机上的host_scalar变量的值拷贝到GPU上声明的__constant__变量MY_SCALAR_CONSTANT。