微内核操作系统移植指南:从x86到ARM

关键词:微内核、操作系统移植、x86架构、ARM架构、硬件抽象层、系统调用、中断处理

摘要:本文详细介绍了如何将微内核操作系统从x86架构移植到ARM架构的全过程。我们将从微内核的基本概念讲起,逐步深入到架构差异分析、移植策略制定、关键组件适配等核心环节,最后通过实际案例展示完整的移植流程。无论您是操作系统开发者还是嵌入式系统工程师,都能从本文中获得实用的移植技巧和方法论。

背景介绍

目的和范围

本文旨在为操作系统开发者提供一份完整的微内核系统移植指南,重点讲解从x86到ARM架构的移植过程。我们将覆盖从理论到实践的各个环节,包括架构差异分析、关键组件适配、测试验证等。

预期读者

本文适合以下读者:

操作系统内核开发人员

嵌入式系统工程师

计算机科学相关专业学生

对操作系统移植感兴趣的技术爱好者

文档结构概述

首先介绍微内核的基本概念和特点

分析x86和ARM架构的关键差异

详细讲解移植的核心步骤和策略

通过实际案例展示完整移植流程

讨论常见问题和优化技巧

术语表

核心术语定义

微内核:一种操作系统设计方法,将核心功能最小化,其他服务运行在用户空间

移植:将软件从一种硬件平台迁移到另一种硬件平台的过程

ABI:应用程序二进制接口,定义程序与操作系统之间的调用约定

相关概念解释

硬件抽象层(HAL):隔离硬件差异的软件层

交叉编译:在一个平台上生成另一个平台可执行代码的过程

引导加载程序:初始化硬件并加载操作系统的程序

缩略词列表

HAL:Hardware Abstraction Layer

ABI:Application Binary Interface

MMU:Memory Management Unit

IRQ:Interrupt Request

核心概念与联系

故事引入

想象你是一位乐高大师,设计了一套精美的乐高城堡(微内核操作系统)。现在你要把这套城堡从标准的乐高底板(x86平台)搬到一种新的特殊底板(ARM平台)上。虽然两块底板都能搭建城堡,但它们的固定方式、连接结构都不同。你需要重新设计一些连接件,调整部分结构,但保持城堡的核心功能和外观不变。这就是操作系统移植的本质!

核心概念解释

核心概念一:微内核架构

微内核就像一位高效的经理,只负责最核心的工作(进程调度、内存管理等),其他任务(文件系统、设备驱动等)都交给专门的”员工”(用户态服务)处理。这种设计使得系统更加模块化,便于移植和维护。

核心概念二:硬件抽象层(HAL)

HAL就像一位翻译官,将不同硬件平台的”方言”翻译成内核能理解的”普通话”。通过HAL,内核可以不用关心底层硬件的具体细节,大大简化了移植工作。

核心概念三:交叉编译工具链

这就像一套特殊的乐高工具,让你能在x86电脑上搭建出能在ARM平台上运行的代码。它包含编译器、汇编器、链接器等组件,是移植工作的基础工具。

核心概念之间的关系

微内核和HAL的关系

微内核通过HAL与硬件对话。就像经理通过翻译与外国客户沟通,HAL让微内核无需学习每种硬件的”语言”就能控制它们。

HAL和交叉编译工具链的关系

交叉编译工具链为HAL生成正确的机器代码。就像翻译需要正确的字典,HAL需要针对目标平台编译的代码才能正常工作。

微内核和交叉编译工具链的关系

微内核的源代码需要通过交叉编译工具链转换为目标平台的可执行文件。就像经理的指令需要转换成员工能理解的形式才能执行。

核心概念原理和架构的文本示意图

+-----------------------+

| 用户态服务 |

| (文件系统、网络栈等) |

+-----------------------+

↓

+-----------------------+

| 系统调用 |

+-----------------------+

↓

+-----------------------+ +-----------------------+

| 微内核 | ←→ | 硬件抽象层 |

| (进程、内存、IPC管理)| | (隔离架构差异) |

+-----------------------+ +-----------------------+

↓

+-----------------------+

| 硬件平台 |

| (x86/ARM等) |

+-----------------------+

Mermaid 流程图

核心算法原理 & 具体操作步骤

1. 架构差异分析

x86和ARM架构的主要差异包括:

指令集架构:

x86使用CISC指令集,ARM使用RISC指令集

寄存器组织和用途不同

内存访问模型差异

中断处理:

中断控制器设计不同(x86使用APIC,ARM使用GIC)

中断向量表结构差异

内存管理:

页表结构不同

TLB管理方式差异

系统启动:

引导流程差异

早期硬件初始化序列不同

2. 交叉编译环境搭建

以GCC工具链为例:

# 安装ARM交叉编译工具链

sudo apt-get install gcc-arm-linux-gnueabihf

# 验证工具链

arm-linux-gnueabihf-gcc --version

# 配置内核编译环境

export ARCH=arm

export CROSS_COMPILE=arm-linux-gnueabihf-

3. 引导加载程序移植

ARM平台通常使用U-Boot作为引导加载程序。需要配置以下关键参数:

/* U-Boot板级配置示例 */

#define CONFIG_SYS_TEXT_BASE 0x87800000

#define CONFIG_SYS_LOAD_ADDR 0x80800000

#define CONFIG_SYS_MALLOC_LEN (16 * 1024 * 1024)

4. 硬件抽象层适配

HAL适配的关键接口:

// 中断控制器接口

struct arm_gic_ops {

void (*enable_irq)(int irq);

void (*disable_irq)(int irq);

void (*ack_irq)(int irq);

};

// 定时器接口

struct arm_timer_ops {

void (*init)(uint32_t freq);

uint64_t (*read_counter)(void);

};

// 内存管理接口

struct arm_mmu_ops {

void (*init)(void);

void (*map)(vaddr_t virt, paddr_t phys, size_t size, uint32_t flags);

};

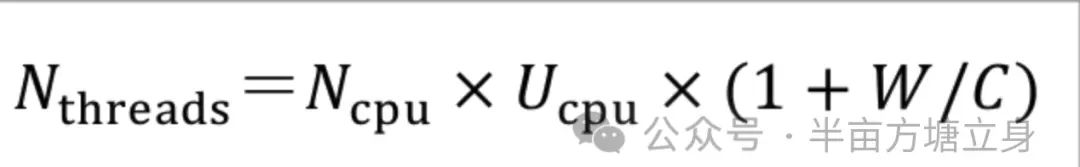

数学模型和公式

1. 内存地址转换

ARM架构使用两级或三级页表转换。虚拟地址到物理地址的转换公式:

物理地址=TTBR+(VirtualAddr[N:M]×页大小)+VirtualAddr[M-1:0] ext{物理地址} = ext{TTBR} + ( ext{VirtualAddr}[ ext{N:M}] imes ext{页大小}) + ext{VirtualAddr}[ ext{M-1:0}] 物理地址=TTBR+(VirtualAddr[N:M]×页大小)+VirtualAddr[M-1:0]

其中:

TTBR:转换表基址寄存器

N:M:页表索引位

M-1:0:页内偏移

2. 中断延迟计算

微内核的中断延迟由以下因素决定:

中断延迟=最大关中断时间+上下文切换时间+调度延迟 ext{中断延迟} = ext{最大关中断时间} + ext{上下文切换时间} + ext{调度延迟} 中断延迟=最大关中断时间+上下文切换时间+调度延迟

在ARM架构上,典型的中断延迟应控制在10-100微秒范围内。

项目实战:代码实际案例和详细解释说明

开发环境搭建

硬件准备:

开发主机:x86_64 Linux系统

目标板:ARM Cortex-A系列开发板

调试工具:J-Link或OpenOCD

软件准备:

交叉编译工具链

QEMU模拟器(用于前期测试)

串口调试工具

源代码详细实现和代码解读

1. 上下文切换实现

/* ARM架构上下文切换汇编代码 */

.globl arm_context_switch

arm_context_switch:

/* 保存当前上下文 */

push {r4-r11, lr}

str sp, [r0] /* 保存旧任务栈指针 */

/* 加载新上下文 */

ldr sp, [r1] /* 加载新任务栈指针 */

pop {r4-r11, lr} /* 恢复寄存器 */

bx lr /* 返回到新任务 */

2. 中断处理适配

/* ARM GIC中断控制器驱动 */

void gic_init(void)

{

/* 初始化GIC分发器 */

writel(0x1F, GICD_CTLR); /* 启用中断 */

/* 设置所有中断的优先级 */

for (int i = 0; i < GIC_MAX_IRQ; i += 4) {

writel(0xA0A0A0A0, GICD_IPRIORITYR + i);

}

/* 启用CPU接口 */

writel(0x1E0, GICC_PMR); /* 设置优先级掩码 */

writel(0x1, GICC_CTLR); /* 启用CPU接口 */

}

/* 中断处理入口 */

void __irq_handler(void)

{

uint32_t irq = readl(GICC_IAR) & 0x3FF;

/* 调用注册的中断处理函数 */

if (irq < MAX_IRQ && irq_handlers[irq]) {

irq_handlers[irq](irq);

}

/* 中断处理完成 */

writel(irq, GICC_EOIR);

}

代码解读与分析

上下文切换:

保存r4-r11寄存器(被调用者保存寄存器)

保存lr寄存器(返回地址)

切换栈指针(sp)

恢复新任务的寄存器上下文

中断处理:

初始化GIC控制器,设置中断优先级

中断到来时读取中断号

调用预先注册的中断处理函数

发送EOI(End Of Interrupt)信号

实际应用场景

嵌入式设备:

智能家居控制器

工业自动化设备

车载信息系统

安全关键系统:

航空航天电子设备

医疗设备控制系统

金融交易终端

教育研究:

操作系统教学实验

计算机体系结构研究

安全隔离技术验证

工具和资源推荐

开发工具:

QEMU:系统模拟器

OpenOCD:片上调试工具

GDB:调试器

参考文档:

ARM Architecture Reference Manual

《ARM System Developer’s Guide》

《Microkernel Construction》

开源项目参考:

seL4微内核

Zephyr RTOS

Fiasco.OC

未来发展趋势与挑战

发展趋势:

多核/众核支持优化

安全隔离技术增强

实时性能提升

技术挑战:

异构计算支持

能效优化

形式化验证

新兴方向:

微内核与RISC-V结合

物联网边缘计算

可信执行环境

总结:学到了什么?

核心概念回顾:

微内核设计将核心功能最小化,便于移植和维护

硬件抽象层是屏蔽架构差异的关键组件

交叉编译工具链是移植工作的基础

概念关系回顾:

微内核通过HAL与不同硬件平台交互

交叉编译工具链为特定架构生成可执行代码

引导加载程序是系统启动的第一个软件组件

思考题:动动小脑筋

思考题一:

如果要将微内核移植到RISC-V架构,与ARM移植相比,哪些工作可以简化,哪些会更复杂?

思考题二:

在设计硬件抽象层时,如何平衡通用性和性能?请举例说明。

思考题三:

在多核ARM处理器上,微内核的调度器设计需要考虑哪些特殊因素?

附录:常见问题与解答

Q1:移植过程中遇到未定义的指令错误怎么办?

A1:检查交叉编译工具链是否匹配目标架构,确认编译选项是否正确设置了目标CPU类型。

Q2:系统启动后立即崩溃可能是什么原因?

A2:常见原因包括:1) 栈指针初始化错误 2) 早期内存映射不正确 3) 中断向量表位置错误

Q3:如何验证移植后的系统功能完整性?

A3:建议分阶段验证:1) 内核基本功能 2) 内存管理 3) 任务调度 4) 设备驱动 5) 系统调用

扩展阅读 & 参考资料

书籍:

《ARM System-on-Chip Architecture》by Steve Furber

《Microkernel Construction》by Jochen Liedtke

《The Design and Implementation of the FreeBSD Operating System》

论文:

“The Performance of μ-Kernel-Based Systems” (Liedtke, 1997)

“seL4: Formal Verification of an OS Kernel” (Klein et al., 2009)

在线资源:

ARM开发者文档:developer.arm.com

微内核研究:microkerneldude.org

OSDev Wiki:wiki.osdev.org

暂无评论内容